Hindawi Publishing Corporation EURASIP Journal on Embedded Systems Volume 2007, Article ID 48979, 23 pages doi:10.1155/2007/48979

# Research Article

# **Removing Cycles in Esterel Programs**

### Jan Lukoschus and Reinhard von Hanxleden

Department of Computer Science, Christian-Albrechts-Universität zu Kiel, Olshausenstr. 40, 24098 Kiel, Germany

Received 1 June 2006; Revised 14 January 2007; Accepted 6 March 2007

Recommended by Alain Girault

Esterel belongs to the family of synchronous programming languages, which are affected by cyclic signal dependencies. This prohibits a static scheduling, limiting the choice of available compilation techniques for programs with such cycles. This work proposes an algorithm that, given a constructive synchronous Esterel program, performs a semantics-preserving source code level transformation that removes cyclic signal dependencies. The transformation is divided into two parts: detection of cycles and iterative resolution of these cycles. It is based on the replacement of cycle signals by a signal expression involving no other cycle signals, thereby breaking the cycle. This transformation of cyclic Esterel programs enables the use of efficient compilation techniques, which are only available for acyclic programs. Furthermore, experiments indicate that the code transformation can even improve code quality produced by compilers that can already handle cyclic programs.

Copyright © 2007 J. Lukoschus and R. von Hanxleden. This is an open access article distributed under the Creative Commons Attribution License, which permits unrestricted use, distribution, and reproduction in any medium, provided the original work is properly cited.

# 1. INTRODUCTION

One of the strengths of synchronous languages [1] is their deterministic semantics in the presence of concurrency. Synchronicity implies instantaneous interactions between concurrent threads, which makes it possible to write a synchronous program that contains cyclic interdependencies among concurrent threads. Depending on the nature of this cycle, the program may still be valid; however, translating such a cyclic program poses challenges to the compiler. Therefore, not all approaches that have been proposed for compiling synchronous programs are applicable to all valid cyclic programs. Cyclic programs are currently only translatable by techniques that are relatively inefficient with respect to execution time, code size, or both.

This paper proposes a technique for transforming valid, cyclic synchronous programs into equivalent acyclic programs, at the source code level, thus extending the range of efficient compilation schemes that can be applied to these programs. The focus of this paper is on the synchronous language Esterel [2]; however, the concepts introduced here are applicable to other synchronous languages as well, such as Lustre [3].

Next we will provide an introduction to Esterel and cyclic programs, followed by an overview of previous work on compiling Esterel programs and handling cycles. Section 2

describes how to find cycles in an Esterel program, based on the computation of signal dependencies. Section 3 introduces the transformation algorithm, which is the main contribution of this paper. Optimization options are presented in Section 4, experimental results follow in Section 5. The paper concludes in Section 6, including an example of how to apply our transformation to Lustre.

# 1.1. Introduction to the Esterel language

The execution of an Esterel program is divided into discrete temporal *instants*, or *(logical) ticks*. In such an instant, the Esterel program communicates via *signals* with the environment and different parts of the program itself. In each instant, a signal can be in one of two states: *present* or *absent*. If a signal is *emitted* in one instant, it is considered present from the beginning of that instant on. If a signal is not emitted in one instant, it is considered absent. All parts of the program have in each instant, the same view of all signal states emitted anywhere in the entire program.

The Esterel language consists of *kernel statements* and *derived statements*. As the latter are essentially "syntactic sugar" and can be derived from the former, we will restrict our attention here to kernel statements. The draft book [4] by Berry on the Esterel semantics provides a list and reasoning on the selection of kernel statements. Some example Esterel

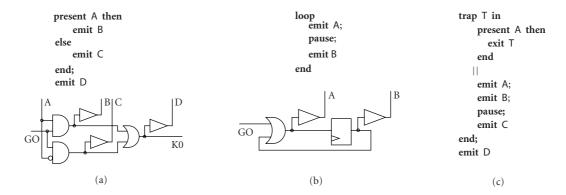

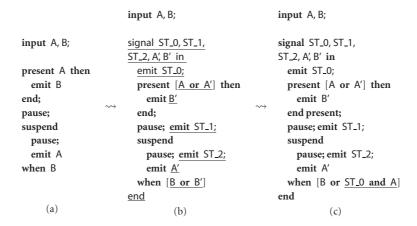

FIGURE 1: Three Esterel fragments and, for the first two, their translations into circuits.

program fragments are listed in Figure 1. The program in Figure 1(a) starts with a present statement that tests the state of signal A. If A is present, then the then branch is executed, which executes an emit statement that sets the state of signal B to present. Conversely, if A is absent, then the else branch sets C to present. Both branches terminate at the end of the present statement, and in both cases the emit D statement is executed.

Due to its deterministic and synchronous nature, the Esterel language is not only suitable as a programming language, but can also be used for the specification and synthesis of synchronous sequential logic circuits. To give an example, the circuits in Figures 1(a) and 1(b) depict the circuit translations of the respective Esterel codes, according to the circuit semantics [4]. The GO wire starts the circuit and via the KO wire the circuit signals its termination.

Figure 1(b) contains two further structural parts of Esterel: loop and pause. A loop infinitely restarts its enclosed statement block when it terminates. The pause statement stops the execution for the remainder of the current instant and resumes execution in the following instant. The program fragment in Figure 1(b) has the following behavior: in the first instant, the loop starts its body, which executes the emit A statement. The pause statement stops the execution and nothing more happens for the remainder of the first instant. In the second instant, emit B is executed and the loop body terminates; however, the loop body is instantaneously restarted, emit A is executed again and pause is encountered again. For all the following instants the behavior of the second instant is repeated. Regarding the circuit translation, note how the pause gets translated into a register, which delays the GO input to the emission of B.

Figure 1(c) contains a trap and parallel threads as new elements. The trap statement consists of the definition of a trap signal (here T), which acts as an exception, and a body as a scope of that signal. The body may contain an exit T statement to activate the exception signal T. The control flow does not continue after the exit statement but after the entire trap statement. The behavior of trap and exit thus corresponds to catch and throw, respectively.

The trap body in the example in Figure 1(c) contains two parallel threads, separated by the concurrency operator ||.

The parallel thread block terminates when all parallel threads are terminated. In the example in Figure 1(c), signal A is tested in the first thread, while it is emitted in the second thread. Since a signal's status must be consistent in the entire program for an instant, it follows that the emission of A must happen before it is tested in the first thread. Now the first thread is able to test A successfully, the exit T statement is executed. This signals to all other active threads in the associated trap T block to cease execution at reaching the next pause statement this corresponds to a *weak abortion*. As a consequence the second thread executes the emit B statement too. On reaching the pause statement control jumps immediately to the end of the trap block and executes the emit D statement.

Another type of control flow available in Esterel is a temporal delay of execution by a suspend statement:

#### suspend p when S

The execution of code block p is suspended for all those instants when the signal expression S is evaluated to true. An exception is the first instant when entering p, in that instant, S is not evaluated and no suspension takes place.

Figure 2(a) contains an Esterel program including an interface to the environment. Keywords input and output indicate the data direction of interface signals. The states of input signals are read from the environment at the beginning of each instant. Output signals carry their status from the Esterel program to the environment at the end of each instant. Note that input signals may also be emitted internally, and that output signals may be tested.

#### 1.2. Cyclic programs, constructiveness

To illustrate the problem to be solved by the code transformation presented in this paper, we now introduce the concept of *cyclic programs*. We do this rather informally here, and adopt the terminology used in the Esterel primer [5, Chapter 5]. A more detailed treatment follows in Section 2.

As stated in the primer, the availability of instantaneous broadcasting and control transmission makes it possible to write syntactically correct but semantically nonsensical programs.

```

module PAUSE_CYC:

module PAUSE_PREP:

module PAUSE_ACYC:

module PAUSE_OPT:

input A, B;

input A, B;

input A, B;

input A, B;

output C;

output C;

output C;

output C;

signal A_, B_, ST_0,

signal A_, B_, ST_0,

present A

ST_1, ST_2 in

ST_1, ST_2 in

signal A_, B_ in

emit ST_0;

then emit B

emit ST_0;

end;

present A

present [A or

then emit B_

present [A or A_]

pause;

present B

then emit B_

(ST_1 and (B or ST_0))]

then emit A

pause:

then emit B_

present [B or B_]

end

pause; emit ST_1;

present [B or B_]

pause; emit ST_1;

then emit A_

present B

present [B or B_]

end

then emit A_

then emit C

then emit A_

present [B or B_]

end

end

end module

present [B or B_]

then emit C

present [B or B_]

then emit C

end

end

then emit C

end signal

end module

end signal

end module

end signal

end module

(b)

(d)

(a)

```

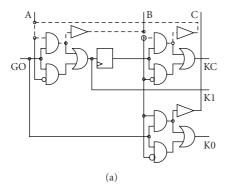

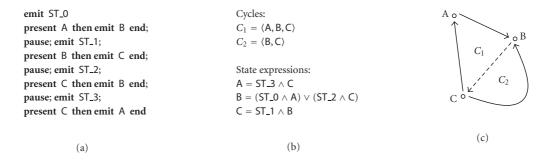

FIGURE 2: Resolving a cycle: (a) original program with cycle between A and B, (b) introduction of state signals and shifting the cycle on internal signals, (c) replacement of cycle signal A\_ by an expression, (d) optimized version.

A simple example for such a nonsensical program is:

#### present A else emit A end

If A is not present at the signal test, then the else part is executed and A is emitted, which invalidates the former signal test. Such a program is considered *nonreactive*, as it does not produce a well-defined output (A can be neither absent nor present). Replacing the else by a then in this example would produce a program that would yield more than one possible output (A could be either absent or present), which would be considered *nondeterministic*. Both variants of this example involve an *instantaneous dependency cycle* between A and itself, and both programs are considered *logically incorrect* and should be rejected by the compiler.

Considering the example above, one might conclude that all programs that contain dependency cycles should be rejected, and the Esterel v4 compiler did just that [6]. However, now consider the program PAUSE\_CYC in Figure 2(a). This program also contains a dependency cycle, involving mutual dependencies between A and B. At run time, however, the dependencies are separated by a pause statement into separate execution instants. The emission of B in the first instant has no effect on the test for B in the second instant. In such a case, where not all dependencies are active in the same execution instant, this is considered a false cycle [5]. Another classic example of a cyclic, yet meaningful program, is the token ring arbiter, shown in Figure 8 [7, 8]. The arbiter also contains a false cycle, and, even more problematic from a compiler's point of view, it does not even allow a static scheduling of the execution order.

We would like to accept programs such as PAUSE\_CYC, and the Esterel v5 compiler does so by establishing that unique values for all signals can be determined in all execution contexts. The v5 compiler accepts all programs that are

constructive [4], meaning that it forbids speculative reasoning, and restricts itself to fact-to-fact propagation according to the imperative nature of Esterel. An analogy in hardware circuitry is that a constructive Esterel program can be directly translated into a circuit where all wires reach unique, predefined voltage levels, irrespective of initial levels and propagation delays.

It is now generally agreed upon that constructive Esterel programs are meaningful, irrespective of whether they are cyclic or not. However, cyclicity poses a particular compilation challenge in that it prevents a compiler from establishing a static ordering for determining the signal values. As elaborated further in Section 1.3, this unfortunately precludes the application of the simulation-based compilation approaches, which are currently the most competitive in terms of execution speed and size. This is where the transformation presented in this paper steps in: it transforms cyclic, constructive programs into equivalent, acyclic programs, such that they are amenable to compilation also by the efficient compilers that require acyclicity.

As discussed further in Section 2.3, different compilers may have different notions of what constitutes a cycle, and whether they are able to handle specific cycles or not. Our code transformation is concerned with transforming constructive programs that are not schedulable by (some) compilers, due to (false) dependency cycles, into equivalent, schedulable programs. To make our transformation widely applicable, we are fairly conservative with respect to what constitutes a dependency and hence may lead to a cycle, and we completely eliminate all cycles even if a smart compiler might be able to determine them to be false.

The key observation, which the transformation presented here builds on, is that if a program is constructive, we can safely *break* a (false) cycle by replacing one of the signals

FIGURE 3: Circuit representation of the program PAUSE\_CYC in Figure 2 (simplified without synchronizer): (a) cycle path of the original program PAUSE\_CYC, (b) transformed, acyclic program PAUSE\_OPT with new local signals A\_ and B\_.

contained in the cycle by a fresh signal. Consider the program PAUSE\_OPT in Figure 2(d). This program is equivalent to PAUSE\_CYC, but the dependency cycle is broken by replacing the emission of B within the cycle by a fresh signal B\_. This can also be seen at the circuit level, see Figure 3; the netlist for PAUSE\_CYC contains a feedback loop, which disappears in the netlist for PAUSE\_OPT. To preserve program equivalence, tests for B outside of the cycle must test for B\_ as well. However, inside the cycle, it suffices to just test for emissions of B (outside of the cycle), thus breaking the dependency cycle. The transformation mechanism presented here aims to automatically produce such equivalent, acyclic programs.

# 1.3. Related work

Today there exist three basic compilation techniques to synthesize code for a general purpose processor: automata, circuit, and event-based code synthesis. The automata-based Esterel v3 compiler developed by Berry and Gonthier [2] unfolds all parallel activities in the source program into a finite automaton with a single point of control. This removes all internal signaling (including cyclic dependencies) with the benefit of a very fast execution of the program. The drawback of this method is a possible state explosion for programs with many parallel threads.

The next generation of the Esterel compiler at Berry's group, the v4, implemented a different strategy. It is derived

from hardware synthesis and is based on the simulation of circuits as the ones shown in Figure 1 in software [4]. This method translates parallelism in Esterel programs into parallel circuits, thus avoiding the state explosion of the automata code compiler. If the synthesized circuit contains cycles, then a dynamic schedule may be needed for the software simulation of the circuit and is therefore rejected by most Esterel compilers that use this approach.

Malik [9] describes a method to transform these cyclic circuits into acyclic ones. It is based on an iterative algorithm to compute the outputs of cyclic circuits with ternary simulation. Effectively the simulation run is serialized into an unfolding of the cycle path until the remaining inputs have no influence on the outputs. These inputs are replaced by constants, making the circuit acyclic. Shiple et al. [10] have developed Malik's work further by applying optimizations and incorporating cycles including registers into the algorithm. An implementation of this method is available in the Esterel v5 compiler [11].

A third approach to synthesize software is to generate an event-driven simulator, which breaks the program down into a number of small functional blocks that are conditionally executed. The CEC [12, 13] and SAXO-RT [14] compilers are based on this concept. These compilers tend to produce code that is compact and yet almost as fast as automata-based code. The drawback of these techniques is that so far, they rely on the existence of a static execution schedule. Therefore these efficient simulation-based compilation approaches are generally unable to compile cyclic programs, as already noted in the previous section.

The difficulties in giving a precise differentiation between cyclic and acyclic programs in different compilers (cf. Section 2.3) are also addressed by Potop-Butucaru [15] in his thesis. He identifies different compilation strategies and different internal dependency representations of Esterel programs as the source for discrepancies. Potop-Butucaru proposes to take the circuit synthesis [4] of Esterel programs as a reference and develops changes to his GRC compilation scheme to match the cycle properties of the v5 compiler. That approach is followed here, too, as we use the circuit semantics that underlies the v5 compiler as a reference to identify cycles in Esterel programs.

Besides software synthesis for a general purpose processor and hardware synthesis, the *reactive processing* approach makes use of specialized processors [16, 17]. However, the designs proposed so far also require acyclicity of the given programs, thus they could also benefit from our transformation.

One approach to overcome the limitation to cyclic programs, which is described by Edwards [18], is to unroll the strongly connected components (cycles) of circuits. Esterel's constructive semantics guarantees that all unknown inputs to these strongly connected regions can be set to arbitrary, known values without changing the meaning of the program.

The transformation of cyclic Esterel programs presented here builds on the work on cyclic circuits by Malik [9], Shiple et al. [10], and Edwards [18]. The main difference is that these previous approaches work on an internal representation used by a particular compiler. Our transformation lifts this to the Esterel level, basically by evolving gate duplications into duplications of signal expressions. This makes our approach applicable to Esterel compilers in general, without the need to access their internals.

The key ideas to resolve cycles in Esterel programs were already described previously [8]. However, that earlier work did not cover the identification of cyclic dependencies, the computation of replacement expressions in the context of parallel termination and hierarchic trap blocks. Extensions to the algorithms to cover valued signals and alternative uses for replacement expressions in constructiveness analysis are presented in the dissertation of the first author [19].

The compilation of Esterel cannot only be complicated by cyclic dependencies, but also by *signal reincarnation*, also known as *schizophrenia* [4]. Most compilation schemes are not able to produce correct code for Esterel programs with schizophrenia problems. The code transformation presented in this work is not able to work on schizophrenic programs, either. A simple method to remove schizophrenia from a program involves code duplication, with potentially exponential cost in code size [4]. Several researchers have proposed more efficient cures for schizophrenia in Esterel programs [4, 20, 21]. These approaches work on the source code level, and could thus also be used as a preprocessing step to the transformation presented here.

We generally assume that the input programs that we transform are constructive in Berry's sense [4], as constructiveness is the property exploited by the way our algorithm breaks dependency cycles. However, it should be noted that this constructive semantics is not the only possible semantics for Esterel. More specifically, there have been different proposals as to which types of Esterel programs should be considered valid and which should be rejected. Boussinot has presented a number of alternatives, implemented in the SugarCubes project [22]. Another approach, called *maximal causality analysis*, has been suggested by Schneider et al. [23].

#### 2. DETECTING DEPENDENCY CYCLES

We now refine the concept of program cycles that has been introduced informally in Section 1.2, and present an algorithm to detect such cycles.

### 2.1. Signal dependencies

We say that a signal P *depends* on signal S if, in some instant, for some sequence of input events, the presence or absence of P can only be decided on (according to the constructive semantics) if the presence or absence of S has been established. We then also say that this is a *dependency* from S to P. For a simulation-based compiler (cf. Section 1.3) a dependency represents a scheduling constraint.

The two most basic elements of a signal dependency are the *test* for a signal state (present S) and the *emission* of a signal (emit P). If both elements are combined in a program fragment

# present S then emit P end

then a signal dependency is created; the presence state of S decides about the emission of P. Therefore the state of S must be known before the state of P can be established. In other words, signal S is a *guard* for signal P, or P *depends* on S.

The simple fact that an emit statement is contained in a subblock of a present statement is not a *sufficient* condition for a signal dependency. Consider this program fragment

# present S then emit P; pause; emit Q end

The state of S decides over the emission of P in the same instant, which establishes a dependency between S and P. The emission of P is followed by a pause statement and an emission of signal Q inside the same then branch of the present statement. The pause statement defers the emission of Q to the subsequent instant, therefore the emission of Q is not influenced by the state of S in the same instant. Hence, S is a guard for P but not for Q.

While a signal emission being part of a present block is not a sufficient condition for a signal dependency, it is neither a *necessary* condition. Consider the following fragment:

### present S then nothing end; emit P

In this example the emission of P is not part of the present block, but that block must terminate before the emission can take place. To execute the present block, the state of the signal S must be known. The fact that the then and (implicit) else branches both contain just a nothing statement is not relevant here. The constructive semantics of Esterel demands nonspeculative execution of the program, and the execution of either branches of present and subsequently emit P must be stalled until the state of all the tested signals is established. Therefore signal dependencies are established across sequential execution of statements, too, and S is a guard for P in this example.

Other sources for signal dependencies originate in loops connecting dependencies from the end to the start of the body, watcher expressions of suspend statements, or in exceptional control flows triggered by exit statements.

In the presence of reincarnation, this view requires to differentiate between different signal incarnations [4]. However, as we want to separate the reincarnation problem from the cyclicity problem, we will henceforth assume that signal reincarnation has been resolved by one of the known methods (cf. Section 1.3) before we get to analyze the program, and will assume that signals are unique.

# 2.2. Dependency cycles

We say that a program has a (dependency) cycle, or is cyclic, if there is a cyclic sequence of signal dependencies; this may also be, for example, a self-dependency. A dependency from S to P is active during a specific instant if during that instant the presence of P causally depends on the presence of S.

We say that a cycle is *false* if not all of its constituent dependencies can be active at the same instant. In case we can establish a fixed partial order among the emissions and tests of the signals involved in the cycle, as in the PAUSE\_CYC example, we consider this false cycle to be *statically schedulable*.

Otherwise, it is *dynamically schedulable*, as for example in the token ring arbiter. If a program contains a *true cycle*, this cycle is not schedulable, and the program is not constructive and not considered further here.

#### 2.3. The compiler's view

The definition of "signal dependencies" given in Section 2.1 and the subsequent definitions of cyclicity that build on it refer to the constructive semantics of Esterel, as defined, for example, by the Constructive Behavioral Semantics [4]. Ideally, all Esterel compilers we are concerned with would share exactly this view. There is indeed such a direct link between what we consider a true cycle and the v5 compiler: the v5 compiler, when using its built-in constructiveness analysis (option -causal), should accept a program if and only if it does not contain a true cycle. We have noticed that there are constructive programs (such as mejia [24]) where the constructiveness analysis of the v5 compiler fails; however, these seem to be implementation imperfections (e.g., regarding cycles on valued signals) and do not represent fundamental compiler limitations. Furthermore, these programs can still be compiled and run using the -I option, which generates interpretative code.

The picture becomes less clear when considering cycles in constructive programs, that is, false cycles. For a given program, it is decidable whether the program contains a false cycle or not, according to our definition, again based on Esterel's constructive semantics. Unfortunately, different compilers may have different ideas of what constitutes a (false) cycle, and whether a detected (false) cycle is statically schedulable or not. The Esterel examples discussed so far did not pose any particular problems for a compiler. However, there are other more involved cases that are more difficult for a compiler. Consider the following fragment:

#### [ present S then nothing end || pause ]; emit A

In this example, A does not depend on S, as the pause in the second thread causes the whole parallel statement to pause, thus separating the present S and the emit A into disjoint instants. The CEC does correctly detect that there is no dependency here; however the v5 compiler is unable to perform such reasoning, and assumes a dependency here. Conversely, there are other examples where the CEC detects dependencies that the v5 compiler does not [19]. The underlying reason for these discrepancies is the difference in the internal program representations used by these compilers [15].

Some compilers, such as the SAXO-RT, accept certain cyclic programs if they can establish that all cycles are false. The compiler tries to determine whether a cycle contains *exclusive* dependencies, meaning that they cannot be activated in the same instant, for example, if they belong to different branches of a present test or if they are separated by a pause statement. Thus, the SAXO-RT is able to compile, for example, the PAUSE\_CYC program. However, this fails for cycles which must be dynamically scheduled, such as the aforementioned token ring arbiter.

As compilers in general do not perform an exhaustive causality analysis, they perform conservative approximations

when analyzing dependencies, and when analyzing whether dependency cycles are statically schedulable or not. Therefore, to make our transformation applicable as broadly as possible, while at the same time avoiding unnecessary transformations, it would be ideal if we would transform only those cycles that are rejected by the compiler that is actually used. Therefore that compiler would have to provide details on rejected cycles. However, compilers typically do not provide this information, at least not in a standardized fashion. As part of the algorithm, we detect cycles ourselves before resolving them. The algorithm for doing so is presented in the next section.

#### 2.4. Algorithm to detect dependency cycles

The algorithm presented here is divided into two parts: (1) identification of all direct signal dependencies, and (2) searching for cycles in signal dependencies. The first part is specified as a structural induction on Esterel programs with a set of signal pairs as a result. Each signal pair describes a dependency from one signal to another. These pairs can be interpreted as edges in a directed graph with the signal names as nodes. The second part of the algorithm, the detection of cycles in such a graph, is straightforward.

The method to derive signal dependencies here is based on the Esterel circuit semantics, as also used by the v5 compiler. The plain circuit semantics just defines the expansion of Esterel statements into circuits without any optimizations. The v5 compiler actually performs additional circuit minimization steps on the resulting circuit, for example, by propagating constant input values. This reduces the size of the resulting circuit considerably and is sometimes able to remove signal dependencies that would lead to cyclic dependencies otherwise.

Our method to derive signal dependencies uses no optimizations, primarily because we do not explicitly generate a circuit for the full program, making general logic optimization algorithms not applicable. Furthermore we want to provide a conservative solution for cyclic dependencies, which does not depend on specific optimizations implemented in specific compilers. The drawback of this conservative approach is that cycles may be resolved unnecessarily.

All signal dependencies lead from signal emissions to signal tests. This leads to the basic idea of our approach to search for signal dependencies in Esterel programs.

- (1) The program is recursively traversed.

- (2) Signals in a present condition are added to a set *G* of *guard signals*.

- (3) If an emit statement is encountered, then new dependencies from all signals in *G* to the emitted signal are collected in a global set *D* of signal dependencies.

- (4) *G* is emptied when a pause statement is encountered.

The rule set listed in Algorithm 1 implements the computation of signal dependencies for kernel statements of Esterel. The suspend statement is left out for reasons laid out in the discussion of Step (2d) of the transformation

ALGORITHM 1: Equations to determine signal dependencies from kernel statements. Suspend is replaced by other kernel statements.  $\mathcal{D}$  collects signal dependencies from signal emissions,  $\mathcal{G}$  returns the active guard signals from terminating statement blocks. P stands for the corresponding program fragment shown on the left, G is the set of guard signals, and X is the set of trap signals in the current context.

algorithm in Figure 4. While traversing the syntactical elements of a program P with signals  $\Sigma$ , two sets of active guard signals are maintained.

$G \subset \Sigma$ : set of signals (*guards*) comprising the current present conditions.

$X \subset \Sigma$ : set of trap signals (*exceptions*) in the current scope.

Signals in *X* are kept separate from *G* because trap signals are not removed by pause statements. The rules to derive signal dependencies from Esterel programs are implemented in two

functions (with  $\Pi$  as the set of Esterel programs and  $\Sigma$ as the set of signals):

$$\mathcal{D} \colon \Pi \times 2^{\Sigma} \times 2^{\Sigma} \longrightarrow 2^{\Sigma \times \Sigma} \quad (P, G, X) \longmapsto \mathcal{D}(P, G, X)$$

$$\mathcal{G} \colon \Pi \times 2^{\Sigma} \times 2^{\Sigma} \longrightarrow 2^{\Sigma} \quad (P, G, X) \longmapsto \mathcal{G}(P, G, X)$$

$\mathcal{D}$  computes the signal dependencies from the current guard signals. The result is a set of signal pairs describing all signal dependencies in P. It uses  $\mathcal{G}$  to handle sequences of statements.  $\mathcal{G}$  returns the set of guard signals that are active when the control flow leaves the program block P. To extract the

**Input:** Program P, potentially containing cycles **Output:** Modified program P'', without cycles

- (1) Check constructiveness of *P*. If *P* is not constructive: **Error**.

- (2) Preprocessing of *P*:

- (a) If *P* is composed of several modules, instantiate them into one flat main module.

- (b) Expand derived statements that build on the kernel statements, except for suspend which is handled in Step (2d).

- (c) Rename locally defined signals to make them unique and lift the definitions up to the top level. Furthermore, eliminate signal reincarnation.

- (d) Transform suspend into equivalent present/trap statements.

- (e) Add explicit termination handling to II statements.

- (f) Add emission of individual state signals ST\_i to the start of the program and each pause statement.

- (3) Identification of cyclic signal dependencies:

- (a) Identify all signal dependencies  $D = \mathcal{D}(P, \emptyset, \emptyset)$ .

- (b) If *D*does not contain cycles: **Done**. Otherwise: Select a shortest cycle  $\vec{C}$ , of length *l*.

- (4) Transform P into P'; do for all  $\sigma_i \in \vec{C}$ , if  $\sigma_i$  is an input signal in the module interface:

- (a) Globally declare a new signal  $\sigma'_i$ .  $\sigma'_i$  replaces  $\sigma_i$  in  $\vec{C}$ .

- (b) Replace "emit  $\sigma_i$ " by "emit  $\sigma_i$ "."

- (c) Replace tests for  $\sigma_i$  by tests for " $(\sigma_i \text{ or } \sigma_i')$ ."

- (5) Transform (still cyclic) P' into (possibly acyclic) P'':

- (a) For all  $\sigma_i \in C$  determine replacement expressions  $E_i = \mathcal{E}(P', \mathsf{ST\_0})$  (see Algorithm 2).

- (b) Select some cycle signal  $\sigma_p \in \vec{C}$  as the pivot signal to break the cycle.

- (c) Iteratively transform  $E_p$  to  $E_p^*$  by replacement of all signals  $\sigma_i \in (\vec{C} \setminus \sigma_p)$  by their expressions  $E_i$ .

- (d) Transform  $E_p^*$  into  $E_p^{**}$  by replacing  $\sigma_p$  by false (or true) and minimize result. Now  $E_p^{**}$  does not involve any cycle signals.

- (e) Replace all tests for  $\sigma_p$  in P' by  $E_p^{**}$  resulting in P''.

- (6) Goto Step (3), treat P'' now as P.

FIGURE 4: Transformation algorithm for pure signals.

signal dependencies Dfrom an Esterel program P,  $\mathcal{D}$  is applied to P with initially empty guard sets:  $D = \mathcal{D}(P, \emptyset, \emptyset)$ .

As an example for how our cycle detection mimics Esterel's circuit semantics, consider again the example in Figure 1(a). Here signals B and C are emitted under direct control of signal A, therefore B and C depend on A. This is visible in the circuit as the two and gates that depend on A and control the activation of the signal drivers for B and C. Signal D is emitted in sequence of the present statement. The dependency of D on A is visible in the circuit by following the path through the or gate.

These kinds of dependencies are determined by collecting all signals in present conditions as guard signals. The order of the recursive traversal is set up to mirror the (internal, anonymous) wires connecting the different parts of the cir-

cuit. If a pause statement is encountered, then the guard set *G* is emptied because signal dependencies do not reach over pause statements, which correspond to registers at the circuit level.

The body p of loop is evaluated twice in  $\mathcal{D}$  to capture dependencies resulting from an instantaneous restart of the loop body. In the following example signal B depends on A because of such an instantaneous restart:

# loop emit B; pause; present A then nothing end end

Trap/exit represents a different kind of flow of control than that is followed by the recursive traversal. An exit T statement transfers control to the surrounding trap T environment. Our recursive dependency analysis does not directly follow these exceptional control paths, but instead stores the trap signal as a dependency on the guard set *G*. When the recursive traversal of a trap T body is completed, all currently stored guards on the trap signal are retrieved from the dependency list and put back into the guard set. Additionally all pause statements within a trap T environment connect the current guard set to T to capture dependencies resulting from parallel threads to an exit statement.

The rules in Algorithm 1 contain no optimizations regarding unreachable code. That simplification may lead to the detection and subsequent transformation of cycles which are not rejected by Esterel compilers in the first place. An extended rule set that detects dead code is given in the thesis [19].

# 3. PROGRAM TRANSFORMATION

After identifying cyclic dependencies, we are now able to resolve those cycles by transforming the program as described in the following.

#### 3.1. The base transformation algorithm

Figure 4 presents the algorithm for transforming cyclic Esterel programs into acyclic programs. Each transformation step is discussed along with its worst-case increase in code size. The core of the algorithm is Step (5d), which breaks dependency cycles; however, to do this step, we have to first analyze and preprocess the program. The algorithm presented here is applicable to programs with cycles that involve pure signals only. Extensions to support valued signals as well are presented elsewhere [19].

Step (1): the constructiveness of the Esterel program is a precondition for the transformation. It can be performed using, for example, the methods developed by Berry and by Shiple et al. [4, 10]; one available implementation is offered by the v5 compiler [25]. The constructiveness property is exploited in Step (5d) of the algorithm. Note that as acyclicity implies constructiveness, we may first run an acyclicity test, by the compiler, or by Step (3) of our algorithm, which is generally cheaper than a full constructiveness analysis.

Step (2): the core algorithm is only applicable to Esterel programs that have been preprocessed as follows.

Step (2a): the expansion of modules is a straightforward textual replacement of module calls by their respective body.

No dynamic run time structures are needed, since Esterel does not allow recursions.

Step (2b): regarding the statements handling signals, the transformation algorithm is expressed in terms of Esterel kernel statements. Therefore all derived statements must be expanded to kernel statements.

Step (2c): we have to eliminate locally defined signals because replacement expressions for signals computed by the algorithm could carry references to local signals out of their scope. (Note that the programmer may still freely use local signal declarations.) Furthermore, the method of finding replacement expressions assumes that signals are unique, that is, not reincarnated. To address the problem of reincarnation, algorithms with different efficiency are available [4, 21].

Step (2d): the introduction of state signals fails in the context of suspend statements, because state signals emitted as part of a suspend block are suspended too. This constitutes a dependency of the state signals on the—possibly cyclic—suspension condition and may lead to a new cycle, thus preventing a successful reduction on the number of cycles

The solution proposed here simulates the behavior of suspend blocks by means of other kernel statements (trap, exit, pause, present, loop), which are handled directly. The key difference to the original suspend behavior is the handling of state signals; they are emitted regardless of suspension conditions. This avoids unwanted dependencies for state signals.

Suspension blocks are transformed by removing the suspend envelope:

suspend p when

$$S \rightsquigarrow p'$$

Here p denotes the suspended body and S denotes the suspension condition. They are replaced just by the body p' derived from p, where all pause statements inside p are replaced by "await not S." This transformation emulates the behavior of suspend by explicitly checking the suspension condition at the start of each instant. However, as the await statement is a derived statement, we have to transform it further into kernel statements:

# await not S → pause; present S else exit T end end end

The complexity of this part of the transformation is a constant factor of the number of pause statements inside suspend statements.

When transforming cascaded suspend blocks, then each suspension block can be treated individually. For each suspend definition another layer of trap/loop blocks will be put around included pause statements. The order of transformations of the suspend blocks is not relevant here.

An alternative solution to handle state signals inside suspend blocks, which is based on a small extension to the Esterel language, is proposed in the thesis [19]. It is based on the emission of state signals with no regard for suspension, thus avoiding the introduction of dependencies from the sus-

pend condition to the enclosed state signals introduced in later steps.

Step (2e): another case of hidden program state is present in the termination control of parallel statements. Consider a parallel block with two threads:

$$p \parallel q$$

This parallel block terminates, if both subblocks p and q terminate. The precise signal state of termination of the whole parallel statement is not directly accessible, because threads that are terminated in earlier execution instants do not emit any signals anymore. Therefore a simple signal expression will generally not describe the termination context of parallel statements.

Figure 5 illustrates the addition of auxiliary signals at the end of each thread in a parallel statement. These signals are continuously emitted, once that thread is terminated. An additional thread tests for the conjunction of all these auxiliary signals. If all auxiliary signals are present, then the entire parallel statement is terminated via a trap exception. This transformation replaces the regular termination mechanism of parallel statements by trap exception handling, which is covered by the regular algorithm.

Step (2f): the execution state of an Esterel program is stored in variables defined inside the synthesized code. Unfortunately there is no provision at the Esterel level to access the state of these variables. The introduction of additional state signals makes the current state of the program available to signal expressions. Each pause statement is supplemented with the emission of a unique signal "pause; emit ST\_i." The emission of the first state signal "emit ST\_0;" is added to the program start. ST\_0 corresponds to the boot register in the circuit representation of Esterel programs. Note that many of the signals may be eliminated again by subsequent optimizations, see Section 4.

Step (3): cycles in the program are identified by building a graph representing the control flow dependencies between present tests and signal emissions. That directed graph is used to search for cyclic dependencies in the Esterel program. Only signals which are part of the currently resolved cycle are of further interest. More details on the detection of cyclic dependencies are given in Section 2.4. If there is more than one cycle present in the program, then Steps (4) and (5) are performed for each cycle individually. In each cycle resolving step the currently smallest cycle must be selected to be resolved. This ensures the termination of the iterative expression transformation in Step (5c).

The signals comprising the currently selected cycle are called *cycle signals* in the following.

Step (4a/4b): this step splits each cycle input signal  $\sigma_i$  into two signals  $\sigma_i$  and  $\sigma_i'$ . Input signals to/from sub-modules are not addressed here, only the connections to the environment. The motivation of this step is to distinguish between emissions from inside the Esterel program and from the environment. The signal with the original name  $\sigma_i$  is under the control of the environment. All signal emissions in the program itself use the new signal name  $\sigma_i'$ . The aim of

```

signal T_i, T_j in trap T in

signal T_i, T_j in

p;

trap T in

loop

emit T_i; pause

p;

sustain T_i

end

q;

a:

sustain T_j

loop

\parallel

emit T_j; pause

end

present [T_i and T_j]

then exit T end;

present [T_i and T_j]

end

then exit T end;

end

end

end

end end

(a)

(b)

(c)

```

FIGURE 5: Making the termination state of parallel threads visible to signal expressions by continuous emission of auxiliary signals on terminated subthreads: (a) original parallel block with threads p and q, (b) added termination handling by trap, (c) expansion of sustain into kernel statements.

FIGURE 6: Program with potentially nonterminating iterative signal replacement: (a) cyclic program containing two cycles with a common dependency from B to C, (b) cycles and emission contexts of signals, (c) graphical representation of the two cycles, the common dependency is indicated by a dashed line.

the replacement expressions (see Step (5a)) is to substitute tests on cycle signals by expressions made up of noncycle signals. This is not possible for input signals since their behavior cannot be derived from signals in the program. In a way, this introduction of fresh signals, which are emitted exclusively in the cycle, is akin to static single assignment (SSA) [26].

Step (4c): all tests for cycle input signals in the original program are extended by tests for their replacement signals. Using the SSA analogy, this corresponds to a  $\phi$ -node [26].

Step (5a): the computation of replacement expressions *E* is described in detail in Section 3.2.

Step (5b): one signal in the set of cycle signals must be selected as a point to break the cyclic dependency. Any signal in the cycle will work; for example, we may select the signal that generates the smallest replacement expression as computed in the next step.

Step (5c): the replacement expression  $E_p$  for the selected cycle signal  $\sigma_p$  contains references to other cycle signals  $\sigma_j$ . These are recursively replaced by their respective expressions

$E_j$  into  $E_p^*$ . This unfolding of expressions is performed until only  $\sigma_p$  and noncycle signals are referenced in  $E_p^*$ .

For Esterel programs containing multiple overlapping cycles that unfolding may not terminate. Figure 6 contains an example for such problematic cycles. If  $C_1$  is selected as the first cycle to resolve, then the iteration will not terminate by oscillating between the replacement and reintroduction of B and C. As a simple remedy it suffices to always select the currently *smallest* cycle in Step (3). The following argues the validity of generally solving the termination problem of the iteration by selecting a smallest cycle.

Preconditions 1. Given constructive Esterel program P, including n cycles  $\vec{C}_1, \ldots, \vec{C}_n$  involving signals  $\sigma_i \in \Sigma$ , one shortest cycle  $\vec{C}_k$  is selected such that for all  $i \in \{1, \ldots, n\}$ :  $|\vec{C}_k| \leq |\vec{C}_i|$ . The emission contexts of all cycle signals  $\sigma_i \in \vec{C}_k$  are represented by expressions  $E_i$  ( $i \in \{1, \ldots, |\vec{C}_k|\}$ ). One signal  $\sigma_p \in \vec{C}_k$  with associated expression  $E_p$  is arbitrarily

selected as the pivot element to break the cycle and perform the iteration.

**Theorem 1.** The iterative replacement of cycle signals  $\sigma_i \in C_k$   $(i \neq p)$  in expression  $E_p$  by expressions  $E_i$  terminates after a finite number of steps.

*Proof.* The occurrences of signals in expressions relate to signal dependencies found in the cycle analysis step: if an expression  $E_i$  for a signal  $\sigma_i$  contains a signal  $\sigma_j$ , then a dependency  $\langle \sigma_j, \sigma_i \rangle$  exists. Dependencies on state signals are omitted here because they are not part of any cycle by design. The iterative replacement of all cycle signals by their respective expressions stops at signal  $\sigma_p$ . This iteration is structurally equivalent to a reverse traversal on the signal dependencies starting from  $\sigma_p$  with the following restrictions: only those signal dependencies are followed where both signals in the dependency are part of the cycle, the traversal stops if  $\sigma_p$  is reached.

The traversal does not terminate if a loop in signal dependencies is encountered. Two cases exist for such loop structures.

A single signal dependency may directly connect an already visited cycle signal to the current cycle signal. Together with the already traversed dependencies this constitutes a cycle with fewer signals than  $\vec{C_k}$ . That is, a contradiction to the precondition on selecting the shortest cycle to resolve first.

The other case is a chain of two or more dependencies connecting back to the cycle. The signals connected by this chain cannot be part of cycle  $\vec{C_k}$  (besides the first and last signals in the chain) because otherwise they would be identical to dependencies already included in  $\vec{C_k}$  or are covered by the previous case. Therefore in this case only signals outside the cycle are covered. Since such signals are not traversed in the iteration, no loop in the iteration is present here.

The complexity of the replacement expressions depends on the length of the cycle, because the length of the cycle governs the number of replacement iterations needed to eliminate all but the first cycle signals in the guard expression. The length of the cycle and the size of each replacement are limited by the number of signals in the program. So there is a quadratic relationship of the size of the replacement expression to the program size. The number of times the replacement expression will be inserted in the program is likewise dependent on the program size. Thus the potential growth in program size for one cycle is of cubic complexity.

Step (5d): this is the central step of the transformation. Since the program is known to be constructive, it follows that  $\sigma_p$  in  $E_p^*$  must not have any influence on the evaluation of  $E_p^*$ . Therefore we can replace  $\sigma_p$  in  $E_p^*$  by any constant value (true or false). The resulting expression  $E_p^{**}$  contains only noncycle signals. This replacement of a cycle signal by a constant is described in Malik's work [9] on resolving cycles in cyclic circuits. The following argues the validity of this replacement.

*Preconditions 2.* Given constructive Esterel program P, including cycle involving signal  $\sigma_p$ , and other signals  $\vec{S}$

$\langle s_0, \ldots, s_n \rangle$ , a replacement function  $E_p^*(\sigma_p, \vec{S})$  for signal  $\sigma_p$  is derived as of Step (5c) according to the circuit semantics of Esterel.

**Theorem 2.** P is constructive  $\Rightarrow E_p^*(true, \vec{S}) = E_p^*(false, \vec{S})$  for all reachable  $\vec{S}$

*Proof.* P is constructive, that is, the state of all signals (including  $\sigma_p$ ) can be determined without speculative reasoning for all reachable states of the program. Therefore the status of  $\sigma_p$  can be derived without previous knowledge of the status of  $\sigma_p$ ; in other words,  $\sigma_p$  is not allowed to depend on itself.  $E_p^*$  computes the status of signal  $\sigma_p$  from signals in P including  $\sigma_p$  itself.

Assuming that  $E_p^*$  yields different results for true and false in place of  $\sigma_p$  would make  $E_p^*$  dependent on  $\sigma_p$ . This contradicts the constructiveness of P. Therefore  $E_p^*$  cannot depend on the status of  $\sigma_p$ .

Remark 1. The use of constructiveness here implies strong constructiveness as defined by Shiple et al. [10], that is, even local nonconstructiveness with no influence on output signals is not allowed.

Step (5e): the last transformation step in the algorithm replaces every occurrence of  $\sigma_p$  in present tests by its replacement expression  $E_p^{**}$ . Now we have replaced one signal of the cycle by an expression which does not contain any references to signals of the cycle. Therefore we have *broken* the current cycle  $\vec{C}$ .

Step (6): the transformation algorithm must be repeated until all cycles are resolved, and the upper limit of cycles to resolve is the number of statements in the program (counting signals, conditionals, emissions, etc.).

It is possible to create an Esterel program with an exponential number of cycles on signals by connecting them in a mesh-like structure. These kinds of cycles share signal dependencies, therefore cutting one signal dependency will resolve multiple cycles, reducing the maximum number of iterations down to the number of signals.

On the other extreme lies a program with signal dependencies connecting all signals to every other signal. In this case each cycle must be resolved individually leading to a quadratic effort with regard to the number of signals. But to establish the net of signal dependencies the program itself must represent each individual dependency at least as a single statement. Therefore the number of cycles to resolve is of linear effort relative to the program size.

# Cost of the transformation algorithm

We now analyze the worst-case code size increase that our transformation may induce. We do not consider the constructiveness analysis part of the transformation itself, and, as it is a prerequisite for compilation of cyclic programs in any case, do not consider it in our complexity analysis of the algorithm. (Conversely, our transformation could potentially be used to speed up constructiveness analysis [19].) Similarly, the expansion of modules in Step (2a), which has potentially

exponential cost, and possibly the resolving of reincarnation in Step (2c) must be done by Esterel compilers anyway. Steps (2b) and (2d) to (4c) all introduce a cost of a constant factor to different parts of the Esterel program. Therefore the overall cost of these steps can be summarized to be a constant factor to the size of the entire Esterel input program. In Step (5c) the actual cycle cutting takes place with a cost of cubic complexity.

Overall, a very conservative estimate results in a cost and code size increase of  $\mathcal{O}(n^4)$ , where n is the source program size after module expansion and elimination of signal reincarnations. However, we expect the typical code size increase to be much lower. In fact, we often experience an actual reduction in source size, as the transformation often offers optimization opportunities where statements are removed. As for the size of the generated object code, here the experimental results (Section 5) also demonstrate that the transformation typically results in a code size reduction.

### 3.2. Computing the replacement expressions

One step towards breaking cyclic dependencies in Esterel programs is to replace within the conditions of present tests the name of a certain signal by an expression (Step (5a) of the algorithm). That expression is derived from the control flow contexts of the program where the signal is set by emit statements. This section presents a set of rules to derive these replacement expressions. These rules are based on the logical behavioral semantics rules [4] with the aim of an easy implementation.

The objective of the rules is to obtain replacement expressions for all signals. A replacement expression describes the signal context of each emission for that signal. Therefore as a prerequisite the signal context of each emit statement is needed. These signal contexts are used to derive the replacement expressions. A current signal context expression Sis modified while traversing the Esterel program P. The context expressions at the point of signal emissions are collected and combined into replacement expressions for all cycle signals. The rules to traverse the Esterel program are implemented in two functions (with  $\Pi$  as set of Esterel programs,  $\Sigma$  as the set of signals, and  $\Psi$  as the set of signal expressions):

Function & searches for signal emissions in program P and returns a mapping of signal names to their signal contexts at the point of their emission. The function & takes the signal state context delivered by previous statements, computes the signal state context from substatements, and returns the signal context for evaluation on sequentially following statements. It is used by & as a helper function.

These functions are computed by structural induction over their first argument (an Esterel program); the corresponding definitions for each kernel statement are given in Algorithm 2. To determine the replacement expressions for all signals in a program P, we compute  $E := \mathcal{E}(P, \mathsf{ST\_0})$ , where  $\mathsf{ST\_0}$  denotes the boot signal, present only at startup in the very first instant. The result in E will be a set of pairs.

Each pair consists of a signal name and a signal expression (condition). The expressions describe in which signal context each signal is emitted. Multiple emissions of the same signal result in multiple entries of that signal in *E*. The expressions for the same signals can now be disjuncted to yield a single replacement expression for the emission of each cycle signal:

$$E_i = \bigvee_{\langle \sigma_i, S_i \rangle \in E} S_j. \tag{11}$$

As an example to illustrate how the definitions of  $\mathcal{E}$  and  $\mathcal{S}$  correspond to the behavioral semantics, consider the present statement. The two structurally operational semantics (SOS) rules from the logical behavioral semantics for the present statement, given in Figure 7, select the rule to apply based on the status of the condition signal s and the resulting control flow. The selected rule will add signal emissions and so forth to the resulting context. The corresponding equations for  $\mathcal{E}$  and  $\mathcal{S}(13)$  consider both possible control flow paths, and both paths may add signal emissions to E; however, each signal emission is tied to the condition for that part, thus reflecting the original semantics.

Rule (15) handles the pause statement with associated emission of its state signal. Function & does not return a context expression for the emission of a state signal, because state signals are emitted behind pause statements and are therefore not subject to any signal dependencies by construction. This is needed since state signals are used to represent the state of signal emissions. Additional dependencies could lead to new cycles, spoiling the transformation. Function & replaces the previous state with the name of the current state signal. The state signal is replaced by false, if the sequentially previous command returned false too. The case switch with condition "S = false" is a simple way to optimize for an unreachable pause statement. In that case the program state is kept false in that thread. If the condition is not successfully evaluated for an S with a value of, for example, "false or false," then only some efficiency is lost.

Trap signals are treated differently from regular signals: function  $\mathcal{E}$  in rule (16) (exit) adds the current signal context as an emission context for the trap signal to E. The trap signal name is marked with a prefix "exit" to be able to distinguish it from regular signals. Function  $\mathcal{S}$  in that rule returns false as a signal context state to indicate that sequentially following code is not reachable.

Function & in rule (17) (trap) removes all references to its own trap signal to not interfere with upper trap definitions. Function & in rule (17) implements the task to compute the termination context of the trap statement. It consists of the normal termination part with no exception taking place, given by  $\mathcal{S}(p,S)$ . The signal context states of control flows triggered by exit statements are extracted from the emission context  $\mathcal{E}(p,S)$ . Those signal context states are limited to exit statements referencing the locally defined trap signal  $(\sigma_i = T)$ . The signal contexts of other trap signals  $(\sigma_i \neq T)$  are negated, because they reference upper trap statements with higher priorities. In Esterel it is possible to specify hierarchic trap definitions sharing the same trap signal name. In

Algorithm 2: Equations to determine replacement expressions for signals:  $\mathcal{E}$  collects the signal state context for signal emissions,  $\mathcal{E}$  returns the signal state context of terminating statements, P is the given program fragment shown on the left, and S is the state expression in the current program context.

that case the innermost trap masks the outer trap definition, effectively reversing the priorities. This is similar to local signals masking global signals of the same name. Duplicate trap identifiers are not checked explicitly in rule (17). That problem is deferred to the Esterel parser.

Rule (19) (loop) is interesting in that it is the only one to evaluate its body p twice for different context states. This

is needed to cover instantaneous restarts of the loop body. The first evaluation is performed by function  $\mathcal{S}$  to derive the context state of the terminating body. That expression is added to the current context state to retrieve the signal emissions of p in the second run with function  $\mathcal{E}$ .

Rule (21) (parallel) returns false for the termination context of all parallel statements, because the termination of

FIGURE 7: Logical behavioral semantics of the present statement [4].

parallel statements is assumed to be replaced by the scheme proposed in Figure 5. It replaces the implicit termination of parallel statements by explicit trap exception handling.

Rules for suspend statements are not given in Algorithm 2, because they are assumed to be substituted by means of other kernel statements in Step (2d) of the transformation algorithm.

# 3.3. Example transformations

To illustrate the transformation algorithm we will now apply it to some example Esterel programs.

# 3.4. Transforming PAUSE\_CYC

Applying the algorithm to the example PAUSE\_CYC in Figure 2(a) yields the acyclic program PAUSE\_ACYC in Figure 2(c).

Step (1): PAUSE\_CYC is cyclic but nevertheless constructive, because a pause statement separates the execution of both parts of the cycle.

Steps (2a) to (2d) do not apply to PAUSE\_CYC. Step (2e) is skipped here for brevity. This is valid here, because the termination of the parallel statement does not influence the cycle.

Step (2f): to prepare the removal of the cycle, we first transform PAUSE\_CYC into the equivalent program PAUSE\_PREP, shown in Figure 2(b). It differs from PAUSE\_CYC in the introduction of state signals ST\_0 to ST\_2. Signals A\_ and B\_ are added in Step (4).

Step (3): PAUSE\_CYC contains one cycle:  $C = \langle A, B \rangle$ .

Step (4): the signals carrying the cycle (A and B) have been replaced by fresh signals A<sub>-</sub> and B<sub>-</sub>, which are only emitted within the cycle. All tests for A and B in the original program are replaced by tests for [A or A<sub>-</sub>] and [B or B<sub>-</sub>], respectively.

Step (5a): the computation of replacement expressions for A<sub>-</sub> and B<sub>-</sub> according to Section 3.2 results in

$$A_{-} = ST_{-}1 \wedge (B \vee B_{-}), \tag{22}$$

$$B_{-} = ST_{-}0 \wedge (A \vee A_{-}). \tag{23}$$

The equations for each signal now refer to other cycle signals; note that we consider A and B not cycle signals anymore, as they are not emitted within the cycle anymore. The similarity to a system of linear equations is apparent, and we solve the equations accordingly.

Step (5b): in PAUSE\_PREP, we arbitrarily select A\_ as the signal to break the cycle.

Step (5c): to replace B<sub>-</sub> in (22), substituting (23) into (22) results in

$$A_{-} = ST_{-}1 \wedge (B \vee (ST_{-}0 \wedge (A \vee A_{-}))). \tag{24}$$

This is now an equation which expresses the cycle signal A\_ as a function of itself and other signals that are not part of the cycle; so we have unrolled the cycle.

Step (5d): replacing the self-reference of signal A<sub>-</sub> on the right-hand side of (24) by false (absent) yields:

$$A_{-} = ST_{-}1 \wedge (B \vee (ST_{-}0 \wedge A)). \tag{25}$$

Similarly, for  $A_{-}$  = true (present),

$$A_{-} = ST_{-}1 \wedge (B \vee ST_{-}0). \tag{26}$$

We now have derived two equally valid replacement expressions for A<sub>-</sub>, which do not involve any cycle signal.

Step (5e): finally we are ready to break the cycle in PAUSE\_PREP. For that, we have to replace the signal selected in Step (5b)—in the cycle—by one of the expressions computed in Step (5d), which does not use any of the cycle signals, without changing the meaning of the program. Substituting (26), the simpler of these expressions, for A\_ in PAUSE\_PREP yields the now acyclic program PAUSE\_ACYC shown in Figure 2(c).

The program PAUSE\_OPT in Figure 2(d) is optimized on the insight that ST\_1 cannot be present at the point of its test.

### 3.4.1. Transforming the token ring arbiter

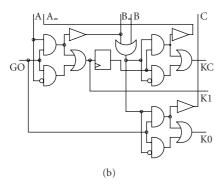

Searching for signal dependencies in the program TR3\_CYC from Figure 8(a) according to the algorithm presented in Section 2 yields the following cycle:

$$C = \langle P1, P2, P3 \rangle. \tag{27}$$

The computation of replacement expressions yields the following results for the cycle signals:

$$P1 = (ST_{-}0 \lor ST_{-}7) \land (T3 \lor P3) \land \overline{R3},$$

$$P2 = (ST_{-}0 \lor ST_{-}1) \land (T1 \lor P1) \land \overline{R1},$$

$$P3 = (ST_{-}0 \lor ST_{-}4) \land (T2 \lor P2) \land \overline{R2}.$$

$$(28)$$

We may select signal P1 to break the cycle. Now the cycle signals P2 and P3 are substituted in the equation for P1:

$$\begin{array}{l} P1 = (ST\_0 \vee ST\_7) \wedge (T3 \vee P3) \wedge \overline{R3} \\ = (ST\_0 \vee ST\_7) \\ & \wedge (T3 \vee ((ST\_0 \vee ST\_4) \wedge (T2 \vee P2) \wedge \overline{R2})) \wedge \overline{R3} \\ = (ST\_0 \vee ST\_7) \\ & \wedge (T3 \vee ((ST\_0 \vee ST\_4) \\ & \wedge (T2 \vee ((ST\_0 \vee ST\_1) \\ & \wedge (T1 \vee P1) \wedge \overline{R1})) \wedge \overline{R2})) \wedge \overline{R3}. \end{array}$$

```

module TR3_CYC:

input R1, R2, R3;

output G1, G2, G3;

signal P1, P2, P3, T1, T2, T3

emit T1

||

||

loop % Station 1

loop % Station 2

loop % Station 3

present [T1 or P1] then

present [T2 or P2] then

present [T3 or P3] then

present R2 then

present R1 then

present R3 then

emit G1

emit G2

emit G3

else

else

else

emit P2

emit P3

emit P1

end

end

end

end:

end:

end:

pause

pause

pause

end loop

end loop

end loop

||

loop

loop

loop

present T2 then

present T3 then

present T1 then

pause;

pause;

pause;

emit T2

emit T3

emit T1

else

else

else

pause

pause

pause

end

end

end

end

end

end

end module

(a)

||

module TR3_ACYC:

loop

present T1 then

input R1, R2, R3;

pause; emit ST_2;

output G1, G2, G3;

emit T2

else

signal ST_0, ST_1, ST_2, ST_3, ST_4,

pause; emit ST_3;

loop % STATION3

ST_5, ST_6, ST_7, ST_8, ST_9 in

end

present [T3 or P3] then

emit ST_0;

end

present R3 then

signal P1, P2, P3, T1, T2, T3 in

emit G3

||

loop % STATION2

else

emit T1

present [T2 or P2] then

emit P1

||

present R2 then

end

loop % STATION1

emit G2

end;

present [T1 or (ST_0 or ST_7) and (T3 or

else

pause; emit ST_7

(ST_0 or ST_4) and (T2 or (ST_0 or ST_1) and

emit P3

end loop

not R1) and not R2) and not R3] then

end

||

present R1 then

end;

loop

emit G1

pause; emit ST_4

present T3 then

else

end loop

pause; emit ST_8;

emit P2

\parallel

emit T1

end

loop

else

present T2 then

pause; emit ST_9

pause; emit ST_1;

pause; emit ST_5;

end

end loop

emit T3

end

else

pause; emit ST_6

end signal

end

end signal

end

end module

(b)

```

FIGURE 8: Token ring arbiter with three stations: (a) Esterel implementation [5] with expanded run modules, (b) acyclic transformation by replacing testing of signal P1.

```

module TrapPause:

module TrapPause:

signal A, B in

signal ST_0, ST_1, ST_2, ST_3,

loop

loop

trap pausais in

ST_4, ST_5 in

emit P_j;

emit ST_0;

loop

pause; emit ST_3

present A then

signal P_i, P_j in

end loop

signal A, B in

emit B

end present;

loop

loop

exit pausais

trap pausais in

present

loop

[P_i and (ST_2 or ST_3)] then

pause;

trap P in

present B then

end present;

emit A

present False then

pause; emit ST_4

end present

emit R

end loop

end loop

end present;

end trap;

exit pausais;

end trap

pause

loop

end loop

end loop

emit P_i;

end trap;

pause; emit ST_1

end signal

pause; emit ST_5

end module

end loop

end loop

end signal

pause; emit ST_2;

end signal

present False then

end signal

emit A

end present;

end module

(a)

(b)

```

FIGURE 9: TrapPause: resolving two cycles between A and B and B on itself: (a) original program, (b) cycles on A and B resolved.

Equation (29) now expresses a cycle carrying signal (P1) as a function of itself and other signals that are outside of the cycle. Again we can employ the constructiveness of TR3\_CYC to replace P1 in this replacement expression by either true or false. Setting P1 to true yields

```

P1 = (ST_0 \vee ST_7)

\wedge (T3 \vee (ST_0 \vee ST_4)

\wedge (T2 \vee (ST_0 \vee ST_1) \wedge \overline{R1}) \wedge \overline{R2}) (30)

\wedge \overline{R3}.

```

Equation (30) is applied when transforming TR3\_CYC into the acyclic program TR3\_ACYC shown in Figure 8(b).

#### 3.4.2. Other example transformations

Figures 9 to 13 list further example transformations that illustrate interesting cases and some subtleties of the transformation problem. Figure 9 lists a program that contains one cycle between signals A and B and another, more complex one involving B across the termination of parallel threads and an additional restart by a loop. Therefore the cycle includes the helper signal P\_j which is introduced to handle the termination of parallel threads.

The program in Figure 10 consists of two parallel threads with a dependency from A to B and vice versa. Several pause statements ensure constructiveness of the program by executing the two dependencies in different instants.

Figure 11 contains program where a cycle is present between signals S and T. Both are contained in a pair of present/emit statements with reversed roles. Constructive-

ness is ensured by mutually exclusive execution of both present statements.

Figure 12 contains a program that features the suspend statement and an input signal A which is part of the cycle. The suspend statement is replaced by a trap/loop construction and the cycle is moved from the input signal to a new internal signal A\_2. The parallel statement is not addressed here because it is not part of the cycle.

In the program in Figure 13, a cycle on signal A is controlled by the termination of two parallel threads. Constructiveness is ensured by separation of emission and test of A in separate instants. The entire parallel part is enclosed in an additional loop structure. This results in an additional cyclic dependency in the termination control of the parallel part. Here constructiveness is ensured by executing a pause statement in at least one parallel thread and therefore separating start and termination of the parallel part into different instants.

#### 4. OPTIMIZATIONS

So far, we have presented the transformation algorithm and equations for replacement expressions in its basic form without any additional improvements. This section outlines some possible optimizations. For space considerations, we here limit the presentation to short descriptions of the most essential optimizations. Further explanations, including examples, and additional optimizations are given elsewhere [19].

# Expression for present

The most important optimization refines the treatment of the present statement in (13). Consider the following

```

module PausePause:

module PausePause:

signal ST_0, ST_1, ST_2, ST_3 in

signal A, B in

pause;

emit ST_0;

signal A, B in

pause;

present A then

emit B

pause; emit ST_1;

pause; emit ST_2;

end present

present False then

pause;

emit B

present B then

end present

emit A

pause; emit ST_3;

end present

end signal

present B then

emit A

end module

end present

end signal

end signal

end module

(b)

(a)

```

FIGURE 10: PausePause: resolving a cycle between A and B: (a) original program, (b) resolved cycle.

```

module TrapParallel:

module TrapParallel:

input A, B;

input A, B;

||

signal ST_0, ST_1, ST_2,

signal S, T in

loop

ST_3, ST_4, ST_5 in

trap X in

present [P_i and P_j] then

emit ST_0;

exit P

signal P_i, P_j in

present A then

end present;

exit X

signal S, T in

pause; emit ST_4

trap X in

end present

end loop

trap P in

present B then

end trap;

present A then

pause

present False then

end present

exit X

emit T

end present;

end present;

present S then

loop

loop

emit P_i;

emit T

pause; emit ST_5

end present;

pause; emit ST_1

end loop

halt

end loop

end trap;

end trap;

present False then

present T then

present B then

emit S

emit S

pause; emit ST_2

end present

end present;

end present

end signal

end signal

loop

end signal

emit P_j;

end signal

end module

pause; emit ST_3

end loop

end module

(a)

(b)

```

FIGURE 11: TrapParallel: resolving two cycles on S and T: (a) original program, (b) resolved cycles.

&((S?p,q),C) = C

(32)

sult in a replacement expression for signal  $C = (ST_3 \land S) \lor (ST_3 \land \overline{S})$ . It is obvious that this can be simplified to

```

module SuspendPause:

module SuspendPause:

module SuspendPause:

input A:

input A:

input A;

output B;

output B;

output B;

signal ST_0, ST_1, A_2 in

suspend

emit A:

emit A;

trap new_trap_0 in

emit ST_0;

pause

loop

when A;

pause;

emit A:

emit B

present A else

trap new_trap_0 in

exit new_trap_0

loop

present B then

pause; emit ST_1;

emit A

end

present [not (A or A_2)] then

end present

end:

exit new_trap_0

emit B

end present

end module

end loop

present B then

end trap;

emit A

emit B

end present

present [ST_1 and not A] then

end module

emit A_2

end present

end signal

end module

(b)

(c)

(a)

```

FIGURE 12: SuspendPause: resolving a cycle between A and B: (a) original program, (b) after substituting suspend, (c) resolved cycle.

if

$$(\mathcal{S}(p, C \wedge S) = C \wedge S) \wedge (\mathcal{S}(q, C \wedge \overline{S}) = C \wedge \overline{S})$$

(33)

holds.

#### Termination of parallel statements

The general transformation algorithm for parallel statements calls for instrumentation to detect the termination of parallel statements at run time. It involves additional signals, sustain statements, and a test for those signals (see Figure 5). These additions are not needed if the parallel statement cannot terminate at all at run time, for example, one thread contains a loop statement on the top level. This is the case for the token ring arbiter (Figure 8(a)).

#### Parallel termination and exceptions