## RESEARCH Open Access

# Efficient embedded architectures for fastcharge model predictive controller for battery cell management in electric vehicles

Anne K. Madsen and Darshika G. Perera\*

## **Abstract**

With the ever-growing concerns about carbon emissions and air pollution throughout the world, electric vehicles (EVs) are one of the most viable options for clean transportation. EVs are typically powered by a battery pack such as lithium-ion, which is created from a large number of individual cells. In order to enhance the durability and prolong the useful life of the battery pack, it is imperative to monitor and control the battery packs at the cell level. Model predictive controller (MPC) is considered as a feasible technique for cell-level monitoring and controlling of the battery packs. For instance, the fast-charge MPC algorithm keeps the Li-ion battery cell within its optimal operating parameters while reducing the charging time. In this case, the fast-charge MPC algorithm should be executed on an embedded platform mounted on an individual cell; however, the existing algorithm for this technique is designed for general-purpose computing. In this research work, we introduce novel, unique, and efficient embedded hardware and software architectures for the fast-charge MPC algorithm, considering the constraints and requirements associated with the embedded devices. We create two unique hardware versions: register-based and memory-based. Experiments are performed to evaluate and illustrate the feasibility and efficiency of our proposed embedded architectures. Our embedded architectures are generic, parameterized, and scalable. Our hardware designs achieved 100 times speedup compared to its software counterparts.

**Keywords:** Embedded architectures, Model predictive control, FPGAs, Hardware accelerators, Electric vehicles, Battery cell management

#### 1 Introduction

The adoption of alternative fuel vehicles is considered as one of the major steps towards addressing the issues related to oil dependence, air pollution, and most importantly climate change. Among many options, electricity and hydrogen fuel cells are the top contenders for the alternative fuel for vehicles. Despite numerous initiatives, both from the government and the private sector around the world, to enhance the usage of electric vehicles (EVs), we continue to face many challenges to promote the wider acceptance of EVs by the general public. Some of these major challenges include charging time of the battery and the maximum driving distance of the vehicle

[1]. In recent years, major EV manufacturers such as Tesla have been making numerous strides in the electric vehicle industry; however, we still have to overcome the distance traveled, high cost, and charging time constraints to gain the market acceptance.

The electric vehicles (EVs) are often powered by energy storage systems such as battery packs, fuel cells, capacitors, super capacitors, and combinations of the above. From the aforementioned energy storage systems, lithium-ion (Li-ion) battery packs are widely employed in EVs mainly because of their light weight, long life, and high energy density traits [2]. In this case, the battery packs are typically created from individual Li-ion cells arranged as series and/or parallel modules. The long-term performance (durability) of the Li-ion battery pack is significantly affected by the choice of the

Department of Electrical and Computer Engineering, University of Colorado at Colorado Springs, 1420 Austin Bluffs Parkway, Colorado Springs, CO 80918, USA

<sup>\*</sup> Correspondence: darshika.perera@uccs.edu

charging strategy. For instance, exceeding the current and voltage constraints of the Li-ion battery cell can cause irreversible damage and capacity loss that would degrade the long-term performance and curtail the effective life of the battery pack [3]. Conversely, operating within the current and voltage constraints would enhance the durability and prolong the useful life of the battery pack. This requires monitoring and controlling the battery packs at the cell level. However, most of the existing research on the battery management system (BMS) focuses on system-level or pack-level control and monitor, as in [2], instead of cell level. Thus, it is crucial to investigate and provide efficient techniques and design methodologies, to monitor and control the battery packs at cell levels and to optimize the parameters of the individual cells, in order to enhance the durability and useful life of the battery packs.

Model predictive controller (MPC) has been investigated as a viable technique for cell-level monitoring and controlling of the battery packs [3]. MPC is a popular control technique that enables incorporating constraints and generating predictions, while allowing the systems to operate at the thresholds of those constraints. For some time, MPC algorithm has been utilized in the industrial processes, typically in non-resource-constrained environments; however, in recent years, this algorithm is gaining interest in the resource-constrained environments, including cyber-physical systems and hybrid automotive fuel cells [3], to name a few. The effectiveness of the MPC algorithm for cell-level monitor/control depends on the accuracy of the mathematical model of the battery cell. These mathematical models include equivalent circuit models (ECMs) and physics-based models. From these, ECM models are more popular due to their simplicity. In [3], the authors prove the efficacy of controlling and providing a fast-charge mechanism for Li-ion battery cells by integrating the MPC algorithm with an ECM model. This fast-charge MPC mechanism incorporates various constraints such as maximum current, current delta, cell voltages, and cell state of charge, which keep the Li-ion battery cell within its optimal operating parameters while reducing the charging time. Thus far, this fast-charge MPC algorithm has been designed and developed in Matlab and executed on a desktop computer [3]. However, in a real-world scenario, it is imperative to execute this fast-charge MPC algorithm on an embedded platform mounted on an individual cell, in order to utilize this algorithm to monitor and control the individual cells in a battery pack.

Since the existing algorithm for the fast-charge MPC is designed for general-purpose computers such as desktops [3, 4], it cannot be executed directly on embedded platforms, in its current form. Furthermore, embedded devices have many constraints, including stringent area

and power limitations, lower cost and time-to-market requirements, and high-speed performance. Hence, it is crucial to modify the existing algorithm significantly in order to satisfy the requirements and constraints associated with the embedded devices.

Although MPC is becoming popular, the measure-predict-optimize-apply cycle [5] of the MPC algorithm is compute-intensive and requires a significant amount of resources including processing power and memory resources (to store data and results). In this case, the smaller the control and sampling interval (or time), the larger the resource cost. This sheer amount of resource cost also impacts the feasibility and efficiency of designing and developing the MPC algorithms on embedded platforms.

We investigated the existing research works on MPC algorithms, as well as the existing research works on embedded systems designs for MPC algorithms in the literature. Most of the research on discrete linearized state-space MPC focused on reducing either the complexity of the quadratic programming (QP) or increasing the speed of the computation of the QP, or both. The existing works on online MPC methods include fast gradient [6, 7], active set [8-10], interior point [11-16], Newton's method [9, 17, 18], and Hildreth's QP [19], and others [20]. In [21], a faster online MPC was achieved by combing several techniques such as explicit MPC, primal barrier interior point method, warm start, and Newton's method. In [9, 18], the logarithmic number system (LNS)-based MPC was designed on a fieldprogrammable gate array (FPGA) to produce integer-like simplicity. The existing research works on embedded systems designs for MPC algorithm focused on FPGAs [8, 11, 12, 17, 22, 23], system-on-chip [9, 16], programmable logic controllers (PLC) [24], and embedded microprocessors [25]. Although there were interesting MPC algorithms/designs among the existing research works, none of the aforementioned existing works were suitable for monitoring and controlling individual cells of the battery pack. For instance, the above existing MPC algorithms/designs did not consist of the feed-through term required by the battery cell model introduced with fast-charge MPC algorithm in [3]. The impact of the feed-through term is discussed in detail in Section 2.

In this research work, our main objective is to create unique, novel, and efficient embedded hardware and software architectures for the fast-charge MPC algorithm (with an input feed-through term) to monitor and control individual battery cells, considering the constraints associated with the embedded devices. For the embedded software architectures, it is essential to investigate and create lean code that would fit into an embedded microprocessor. Apart from the embedded software architectures, we decide to create novel customized hardware architectures for the fast-charge MPC

algorithm (with an input feed-through term) on an embedded platform. Typically, customized hardware is optimized for a specific application and avoids the high execution overhead of fetching and decoding instructions as in microprocessor-based designs, thus providing higher speed performance, lower power consumption, and area efficiency, than equivalent software running on general-purpose microprocessors. In this paper, we make the following contributions:

- We introduce unique, novel, and efficient embedded architectures (both hardware and software) for the fast-charge MPC algorithm. Our architectures are generic, parameterized, and scalable; hence, without changing the internal architectures, our designs can be used for any control systems applications that employ similar MPC algorithms with varying parameters and can be executed in different platforms.

- Our proposed architectures can also be utilized to control the charging of multiple battery cells individually, in a time-multiplexed fashion, thus significantly reducing the hardware resources required for BMS.

- We propose two different hardware versions (HW\_v1 and HW\_v2). With register-based HW\_v1, a customized and parallel processing architecture is introduced to perform the matrix computations in parallel by mostly utilizing registers to store the data/results. With Block Random Access Memory (BRAM)-based HW\_v2, an optimized architecture is introduced to address certain issues that have arisen with HW\_v1, by employing BRAMs to store the data/results. These two hardware versions can be used in different scenarios, depending on the requirements of the application.

- With both hardware versions, we introduce novel and unique sub-modules, including multiply-andaccumulate (MAC) modules that are capable of processing matrices of varying sizes, and distinguishing and handling the sparse versus dense matrices, to reduce the execution time. These sub-modules further enhance the speedup and area-efficiency of the overall fast-charge MPC algorithm.

- Considering the existing works on embedded designs for MPC, our architectures are the only designs (in the published literature) that support a non-zero feed-through term for instantaneous feedback. We perform experiments to evaluate the feasibility and efficiency of our embedded designs and to analyze the trade-offs associated including the speed versus space. Experimental results are obtained in real time while the designs are actually running on the FPGA.

This paper is organized as follows: In Section 2, we discuss and present the background of MPC, including the main stages of the fast-charge MPC algorithm. Our design approach and development platform are presented in Section 3. In Section 4, we detail the internal architectures of our proposed embedded software design and our proposed register-based and memory-based embedded hardware designs. Our experimental results and analysis are reported in Section 5. In Section 6, we summarize our work and discuss future directions.

## 2 Background: model predictive controller

The model predictive controller (MPC) utilizes a model of a system (under control) to predict the system's response to a control signal. Using the predicted response, the control signals are attuned until the target response is achieved, and then, the control signals are applied. For instance, in autonomous vehicles, this model can be used to predict the path of the vehicle. If the predicted path does not match the reference or target path, adjustments are made to the control signals, until the two paths are within an acceptable range.

Our investigation on the existing MPC algorithms revealed that the MPC design in [3] provides a simple, robust, and efficient algorithm for the fast charging of lithium-ion battery cells. Hence, this MPC algorithm [3] could potentially be suitable for creating embedded hardware and software designs. The simplicity of this algorithm is based on two major design decisions that reduce the computational complexity of the algorithm, i.e., to use the dual-mode MPC technique and Hildreth's quadratic programming technique [26].

The dual-mode MPC technique addresses the computational issue of the infinite prediction horizons. This technique divides the problem space into the near-future and the far-future solution segments. This enables the prediction horizons and control horizons to be decreased significantly, while maintaining the performance on par with the infinite prediction horizons [26]. The application of this technique to the fast charge of batteries with a feed-through term is detailed in [26]. As discussed in [26], reducing the prediction horizon dramatically reduces the size of the matrices utilized in MPC, which in turn reduces the computation complexity. Trimboli's group, in [3, 26], evaluated various control horizons and prediction horizons for the optimal performance using the near-future and the far-future approach and determined that the optimal control and prediction horizons to be 1 and 10, respectively.

Hildreth's quadratic programming (HOP) technique is an iterative process that is deemed suitable for the embedded systems designs [27]. This technique is part of the active set dual-primal quadratic programming (QP) solution, which consists of two main features that are beneficial for embedded designs: (1) no matrix inversion is required, hence managing poorly conditioned matrices and (2) the computations are run on scalars instead of matrices, thus reducing the computation complexity [27]. With the HQP, the intention of the MPC is to bring the battery cell to a fully charged position with the least amount of time. In order to reduce the computational effort [3], the pseudo min-time problem is implemented to achieve the same results as the explicit optimal min-time solution. As a result, the HQP technique is deemed appropriate, although it might produce a sub-optimal solution, in case, if the solution fails to converge in the allotted iterations [24]. A recent study [24] revealed that the HQP technique performed faster than the commercial solvers, and it required lean code. However, the main drawback is that it tends to provide the sub-optimal solution more often and is also dependent on selecting the optimal number of iterations. In this study [24], the clock speed per iteration of the HQP technique was approximately 15 times faster than the most robust state-of-the-art active set solver (qpOASES).

The MPC algorithms can be customized to a specific application or a specific task, based on the requirements of a given application/task. The customized MPC typically reduces the execution overhead required for certain decision-making logic that would otherwise be essential for the generalized MPC. Furthermore, embedded architectures are usually designed for a specific application or a specific computation. The above facts demonstrate that the customized MPC algorithms specific to a given model and given constraints are appropriate for embedded hardware/software architectures.

## 2.1 Dynamic model

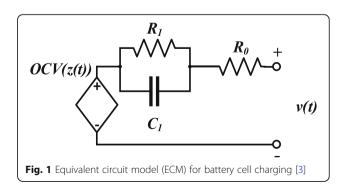

With the MPC algorithm, selecting a suitable model is imperative, since the prediction performance depends on how well the dynamics of the system are represented by the model [28]. For the fast charge of Li-ion batteries in [3], the authors employed an equivalent circuit model (ECM) instead of a physics-based model. The latter models are typically more computationally complex compared to the former models [3]. The sheer simplicity of the ECM leads to a dynamic model that provides a suitable MPC performance for many applications. The ECM model is shown in Fig. 1, and the design and development of the model is detailed in [4, 26].

As illustrated in Fig. 1, the series resistor  $R_0$  is the instantaneous response ohmic resistance, when a load is connected to the circuit. In the ECM model, the  $R_0$  represents the feed-through term in the MPC general state-space Eq. (3) [3, 4, 26]; the  $R_1C_1$  ladder models the diffusion process; the state of charge (SOC) dependent voltage source, i.e.,  $OCV_{z(t)}$ , represents the open circuit voltage (OCV). In this case, the relationship between SOC and OCV is non-linear; thus, it can be implemented as a look-up-table (LUT).

The ECM model has a single control input (i.e., the current) and two measured (or computed) outputs (i.e., the terminal voltage v(t) and the SOC z(t)). The main goal is to bring the battery cell to full SOC with the least amount of time. As a result, the z(t) becomes the output to be controlled, which makes this MPC a single-input single-output (SISO) system. The current i(t), which is the control input signal, is represented in the state-space equations as u(k). By employing the MPC algorithm, our intention is to find the best control input, i(t), in order to produce the fastest charge, while considering the physical constraints of the cell. Typically, the parameters or the of the ECM model are temperature elements dependent.

The creation of our unique and efficient embedded architectures for the MPC algorithm is inspired by and based on the MPC algorithms presented in [3, 4, 26–28], with many modifications to cater to the embedded platforms. The feed-through term and dual-mode adjustments are inspired by and based on the ones in [3, 4, 26].

The state-space equations for the ECM model are designed and developed based on Fig. 1. The physical parameters of the model are  $Q_{(charge)}$ ,  $R_O$ ,  $R_I$ , and  $\tau = R_1C_1$ . In this case, the unaugmented state variables are considered as the z(t), which is the state of charge (SOC) of the open circuit voltage (OCV) and the  $v_{CI}(t)$ , which is the voltage across the capacitor. The terminal voltage v(t) is the output, and the current i(t) is the input control signal. The discretized

state-space variables are  $Z_k$ ,  $v_{C1,k}$ ,  $v_k$ , and  $u_k$ . The general state-space Eq. (1) is presented below:

$$x_{m,k+1} = A_m x_{m,k} + B_m u_k \tag{1}$$

Considering Fig. 1, where  $\Delta t$  is the sampling time and  $\eta$  is the cell efficiency, the model without augmentation [4] is written with the following Eq. (2):

$$\begin{bmatrix} z_{k+1} \\ v_{C_1,k+1} \end{bmatrix} = \begin{bmatrix} 1 & 0 \\ 0 & e^{-\Delta t} / R_1 C_1 \end{bmatrix} \begin{bmatrix} z_k \\ v_{C_1,k} \end{bmatrix} + \begin{bmatrix} -\frac{\eta \Delta t}{Q} \\ R_1 \left( 1 - e^{-\Delta t} / R_1 C_1 \right) \end{bmatrix} u_k$$

$$(2)$$

The general formula for the measured outputs is presented in Eq. (3):

$$y_k = C_m x_{m,k} + D_m u_k \tag{3}$$

where  $D_m$  is the feed-through term, which is a necessary term for the ECM model of this battery.

Next, the output Eq. (4) for the terminal voltage is written as:

$$\nu_{k} = C_{m,\nu} x_{m,k} + D_{m,\nu} u_{k} + OCV(z_{k})

\nu_{k} = \begin{bmatrix} 0 & -1 \end{bmatrix} \begin{bmatrix} z_{k} \\ \nu_{C_{1},k} \end{bmatrix} + \begin{bmatrix} -R_{0} \end{bmatrix} u_{k} + OCV(z_{k})$$

(4)

The general equations for the output to be controlled are presented with the Eqs. (5a) and (5b):

$$z_k = C_{m,z} x_{m,k} + D_{m,z} u_k \tag{5a}$$

In this case, SOC is selected as the output to be controlled and is presented as Eq. (5b):

$$z_k = \begin{bmatrix} 1 & 0 \end{bmatrix} \begin{bmatrix} z_k \\ v_{C_1,k} \end{bmatrix} + \begin{bmatrix} 0 \end{bmatrix} u_k \tag{5b}$$

In this case, the sampling time  $(\Delta t)$  and the cell efficiency  $(\eta)$  are considered as 1 s and 0.997, respectively. These values are determined from [3, 4] based on a Li-ion battery manufactured by the LG Chem Ltd. [4]. Next, the model is augmented to incorporate integral action and the feed-through term. The integral action is incorporated by determining the difference between the state signals  $(\Delta x_{m,k})$  and the control signals  $(\Delta u_k)$ . The final augmented state-space Eqs. (6), (7), (8), and (9) are presented below, based on the design in [3]:

$$\chi_{k+1} = \tilde{A}\chi_k + \tilde{B}\Delta u_{k+1} \tag{6}$$

$$\nu_k = \tilde{C}_{\nu} \chi_k + OCV(z_k) \tag{7}$$

$$z_k = \tilde{C}_z \chi_k \tag{8}$$

where the  $\chi_k$  is defined as follows with Eq. (9):

$$\chi_{k} = \begin{bmatrix} \frac{X_{k}}{u_{k}} \end{bmatrix}, \widetilde{A} = \begin{bmatrix} \frac{A_{m}}{0} & B_{m} \\ 0 & I \end{bmatrix}, \widetilde{B} = \begin{bmatrix} 0 \\ I \end{bmatrix},$$

$$\widetilde{C}_{v} = \begin{bmatrix} C_{m_{v}} & D_{m_{v}} \end{bmatrix}, \text{ and } \widetilde{C}_{z} = \begin{bmatrix} C_{m_{z}} & D_{m_{z}} \end{bmatrix}.$$

$$(9)$$

and also  $x_k = \left[\frac{\Delta x_{m,k}}{y_k}\right]$  from adding the integral action.

#### 2.2 Prediction of state and output variables

Trimboli's group [4, 26] incorporated a feed-through term in the modified MPC algorithm, which was built upon and extended from the work done in [29]. A detailed description of the extended work can be found in [4, 26], and the synopsis of this approach can be found in [3]. For illustration purposes, the summary of this approach is presented below.

After completing the augmented model (from Section 2.1), the gain matrices are computed. To achieve this, the state Eq. (1), as demonstrated below, is propagated to obtain the future states.

$$\chi_{k+1} = \tilde{A}\chi_{k} + \tilde{B}\Delta u_{k+1}$$

$$\chi_{k+2} = \tilde{A}\chi_{k+1} + \tilde{B}\Delta u_{k+2} = \tilde{A}\left(\tilde{A}\chi_{k} + \tilde{B}\Delta u_{k+1}\right) + \tilde{B}\Delta u_{k+2}$$

$$= \tilde{A}^{2}\chi_{k} + \tilde{A}\tilde{B}\Delta u_{k+1} + \tilde{B}\Delta u_{k+2}$$

$$\chi_{k+3} = \tilde{A}^{3}\chi_{k} + \tilde{A}^{2}\tilde{B}\Delta u_{k+1} + \tilde{A}\tilde{B}\Delta u_{k+2} + \tilde{B}u_{k+3}$$

$$\vdots$$

$$\chi_{k+N_{p}} = \tilde{A}^{N_{p}}\chi_{k} + \tilde{A}^{N_{p}-1}\tilde{B}\Delta u_{k+1} + \tilde{A}^{N_{p}-2}\tilde{B}\Delta u_{k+2} + \cdots$$

$$+\tilde{A}^{N_{p}-N_{c}}\tilde{B}u_{k+N_{c}}$$

(10)

Next, the output Eq. (3) is propagated and substituted with the elements of Eq. (4), in order to obtain the predicted output as Eq. (11).

$$\begin{aligned} y_{k+1} &= \tilde{C}\chi_{k,+1} = \tilde{C}\tilde{A}\chi_k + \tilde{C}\tilde{B}\Delta u_{k+1} \\ y_{k+2} &= \tilde{C}\chi_{k,+2} = \tilde{C}\tilde{A}^2\chi_k + \tilde{C}\tilde{A}\tilde{B}\Delta u_{k+1} + \tilde{C}\tilde{B}\Delta u_{k+2} \\ y_{k+3} &= \tilde{C}\chi_{k,+3} = \tilde{C}\tilde{A}^3\chi_k + \tilde{C}\tilde{A}^2\tilde{B}\Delta u_{k+1} + \tilde{C}\tilde{A}\tilde{B}\Delta u_{k+2} \\ &+ \tilde{C}\tilde{B}\Delta u_{k+3} \\ \vdots \\ y_{k+N_p} &= \tilde{C}\chi_{k,+N_p} = \tilde{C}\tilde{A}^{N_p}\chi_k + \tilde{C}\tilde{A}^{N_p-1}\tilde{B}\Delta u_{k+1} \\ &+ \tilde{C}\tilde{A}^{N_p-2}\tilde{B}\Delta u_{k+2} + \dots + \tilde{C}\tilde{A}^{N_p-N_c}\tilde{B}\Delta u_{k+N_c} \end{aligned}$$

$$(11)$$

Rewriting Eq. (11) in matrix form produces the following Eqs. (12) and (13):

$$\mathbf{Y}_{\mathbf{k}} = \begin{bmatrix} \tilde{C} \\ \tilde{C}\tilde{A} \\ \tilde{C}\tilde{A}^2 \\ \tilde{C}\tilde{A}^{N_p-1} \end{bmatrix} \tilde{A}\chi_k \tag{12}$$

$$+\begin{bmatrix} \tilde{C}\tilde{B} & 0 & 0 & \cdots & 0 \\ \tilde{C}\tilde{A}\tilde{B} & \tilde{C}\tilde{B} & 0 & \cdots & 0 \\ \tilde{C}\tilde{A}^2\tilde{B} & \tilde{C}\tilde{A}\tilde{B} & \tilde{C}\tilde{B} & \cdots & 0 \\ \vdots & \vdots & \vdots & \vdots & \vdots \\ \tilde{C}\tilde{A}^{N_p-1}\tilde{B} & \tilde{C}\tilde{A}^{N_p-2}\tilde{B} & \tilde{C}\tilde{A}^{N_p-3}\tilde{B} & \cdots & \tilde{C}\tilde{A}^{N_p-N_c}\tilde{B} \end{bmatrix}$$

$$\begin{bmatrix} \Delta u_{k+1} \\ \Delta u_{k+2} \\ \Delta u_{k+3} \\ \vdots \\ \Delta u_{k+N_c} \end{bmatrix}$$

$$\mathbf{Y}_{\mathbf{k}} = \Phi \tilde{\mathbf{A}} \chi_k + G \Delta \mathbf{U}_k \tag{13}$$

In order to use the far-future control technique, the G matrix and  $\Delta \mathbf{U_k}$  matrix are partitioned into the near-future (nf) and the far-future (ff) elements, where  $G_{nf}$  is a  $N_P \times N_C$  matrix and  $G_{ff}$  is a  $N_P \times N_P - N_C$  matrix as below:

$$\Delta \mathbf{U_k} = \left[ \frac{\Delta \mathbf{U_{k,nf}}}{\Delta \mathbf{U_{k,ff}}} \right], \text{ and } G = \left[ G_{nf} \middle| G_{ff} \right]. \tag{14}$$

As discussed in [4], expressing  $\Delta U_{k,ff}$  in terms of  $\Delta U_{k,nf}$  results in Eq. (15):

$$\Delta \mathbf{U}_{\mathbf{k},\mathbf{ff}} = -(\mathbf{v}\Delta \mathbf{U}_{\mathbf{k},\mathbf{nf}} + u_k) \tag{15}$$

where  $\mathbf{v}_{1 \times N_c} = [1 \ 1 \ 1 \ \cdots \ 1].$

Furthermore, substituting Eq. (13) with the elements of the Eqs. (14) and (15) results in Eq. (16):

$$\mathbf{Y_k} = \Phi \tilde{A} \chi_k + G_{nf} \Delta \mathbf{U}_{k,nf} - G_{ff} \mathbf{v} \Delta \mathbf{U}_{k,nf} - G_{ff} u_k \tag{16}$$

The aforementioned steps are required to process and complete the MPC algorithm. For our embedded architectures, the above equations (from (10) to (16)) remain the same, since the temperature is considered as a constant. There are four temperature-dependent variables, Q,  $R_0$ ,  $R_1$ , and r, utilized in the augmented model. These variables are detailed in Section 4.2.1.

## 2.3 Optimization

With the embedded systems design, our objective is to create a control signal that brings both the output signal  $Y_k$  and the reference or set-point signal  $R_s$  closer together as much as possible. In this case, it is assumed that  $R_s$  remains constant inside our prediction window. The cost function that reflects our optimization goal is written in a matrix form as below:

$$J_k = (\mathbf{Y_k} - \mathbf{R_s})^T (\mathbf{Y_k} - \mathbf{R_s}) + P_1 \Delta \mathbf{U}_{k,nf}^T \Delta \mathbf{U}_{k,nf}. \tag{17}$$

In the above Eq. (17),  $R_s$  is a vector of set-point information, and  $P_I$  is a penalty factor based on the given constants rw and  $\lambda_P$ . Substituting Eq. (17) with the elements of Eq. (16), utilizing properties of the symmetric matrices, and grouping the terms, results in the following cost function:

$$J_{\mathbf{k}} = \Delta \mathbf{U}_{k,nf}^{T} \left( G_{nf}^{T} G_{nf} + P_{1} I - G_{nf}^{T} G_{ff} \mathbf{v} - \mathbf{v}^{T} G_{ff}^{T} G_{nf} + \mathbf{v}^{T} G_{ff}^{T} G_{ff} \mathbf{v} \right) \Delta \mathbf{U}_{k,nf}$$

$$-2\Delta \mathbf{U}_{k,nf}^{T} \left( G_{nf}^{T} \mathbf{R}_{\mathbf{s}} + \mathbf{v}^{T} G_{ff}^{T} \mathbf{R}_{\mathbf{s}} - G_{nf}^{T} \Phi \tilde{A} \chi_{k} - \mathbf{v}^{T} G_{ff}^{T} \Phi \tilde{A} \chi_{k} - G_{nf}^{T} G_{ff} u_{k} - \mathbf{v}^{T} G_{ff}^{T} G_{ff} u_{k} \right)$$

$$+ \left( \Phi \tilde{A} \chi_{k} - \mathbf{R}_{\mathbf{s}} - G_{ff} u_{k} \right)^{T} \left( \Phi \tilde{A} \chi_{k} - \mathbf{R}_{\mathbf{s}} - G_{ff} u_{k} \right). \tag{18}$$

Next, Hildreth's quadratic programming (HQP) technique is used to minimize the above cost function presented in Eq. (18). The input function for the HQP (where x represents the control variable) is written as below:

$$J = \frac{1}{2}x^T E x + x^T F \tag{19}$$

The equality constraint is as follows:

$$Mx \le \gamma$$

(20)

The original function in Eq. (19) is augmented with the equality constraint (presented in Eq. (2) and multiplied by the Lagrange multiplier  $(\lambda)$ ):

$$J = \frac{1}{2}x^{T}Ex + x^{T}F + \lambda^{T}(Mx - \gamma)$$

(21)

In this case, E and F can be inferred from Eq. (18) to produce the following Eqs. (22) and (23):

$$E = 2\left(G_{nf}^{T}G_{nf} + P_{1} - G_{nf}^{T}G_{ff}\mathbf{v} - \mathbf{v}^{T}G_{ff}^{T}G_{nf} + \mathbf{v}^{T}G_{ff}^{T}G_{ff}\mathbf{v}\right)$$

(22)

$$F = -2\left(G_{nf}^{T}\mathbf{R}_{s} + \mathbf{v}^{T}G_{ff}^{T}\mathbf{R}_{s} - G_{nf}^{T}\Phi\tilde{A}\chi_{k} - \mathbf{v}^{T}G_{ff}^{T}\Phi\tilde{A}\chi_{k} - G_{nf}^{T}G_{ff}u_{k} - \mathbf{v}^{T}G_{ff}^{T}G_{ff}u_{k}\right)$$

$$F = -2\left(\left(G_{nf}^{T} + \mathbf{v}^{T}G_{ff}^{T}\right)\mathbf{R}_{s} - \left(G_{nf}^{T} + \mathbf{v}^{T}G_{ff}^{T}\right)\Phi\tilde{A}\chi_{k} - \left(G_{nf}^{T}G_{ff} + \mathbf{v}^{T}G_{ff}^{T}G_{ff}\right)u_{k}\right)$$

$$(23)$$

A weight vector (m) can be added to further enhance the performance of the MPC algorithm. The m vector is a  $1 \times N_P - N_C$  vector that is typically computed offline in Matlab and stored either in registers or in BRAMs. In this case,  $P_2$  is an extra penalty factor added to improve the performance. Since  $N_C = 1$  is utilized,  $\nu$  vector becomes a scalar 1, thus becoming trivial. Considering that the SOC is the output to be controlled and the gain matrices used  $G_z$  and  $\Phi_z$ , then E and F become:

$$E = 2\left(G_{nfz}^{T}G_{nfz} + P_{1} - G_{nfz}^{T}G_{ffz}\mathbf{m} - \mathbf{m}^{T}G_{ffz}^{T}G_{nfz} + \mathbf{m}^{T}G_{ffz}^{T}G_{ffz}\mathbf{m} + \mathbf{m}^{T}\mathbf{m}P_{2}\right)$$

(24)

$$F = -2 \left( \left( G_{nfz}^{T} + \mathbf{m}^{T} G_{ffz}^{T} \right) \mathbf{R}_{s} - \left( G_{nfz}^{T} + \mathbf{m}^{T} G_{ffz}^{T} \right) \Phi_{z} \tilde{A} \chi_{k} \right) - \left( G_{nfz}^{T} G_{ffz} \mathbf{m} + \mathbf{m}^{T} G_{ffz}^{T} G_{ffz} \mathbf{m} + \mathbf{m}^{T} \mathbf{m} P_{2} \right) u_{k}$$

$$(25)$$

Next, the constraints for Eq. (20) are developed, which constrain the control input, the terminal voltage, and the maximum SOC. The developments of M and  $\gamma$  are detailed in [4]; the final Eq. (26) is presented below.

$$M = \left[egin{array}{c} 1 \\ -1 \\ \left(G_{nf

u} + G_{ff

u} \mathbf{m}

ight) \\ -\left(G_{nf

u} + G_{ff

u} \mathbf{m}

ight) \\ \left(G_{nf

u} + G_{ff

u} \mathbf{m}

ight) \end{array}

ight] ext{ and,}$$

$$\gamma = \begin{bmatrix}

u_{\text{max}} - u_k \\

-u_{\text{min}} + u_k \\

\nu_{\text{max}} - \left(\Phi_{\nu} \tilde{A} \chi + G_{ff\nu} \mathbf{m} u_k + OCV\right) \\

-\nu_{\text{min}} + \left(\Phi_{\nu} \tilde{A} \chi + G_{ff\nu} \mathbf{m} u_k + OCV\right) \\

z_{\text{max}} - \Phi_{z} \tilde{A} \chi - G_{ffz} \mathbf{m} u_k

\end{bmatrix}$$

(26)

For the primal-dual approach, the partial derivatives of Eq. (21) are taken, with respect to x and  $\lambda$  as in [4]. In this case, setting the partial derivatives equal to zero and solving the equation for x and  $\lambda$  result in Eq. (27):

$$\lambda = -(ME^{-1}M^{T})^{-1}(\gamma + ME^{-1}F) \tag{27}$$

$$x = -E^{-1}(M^T\lambda + F) \tag{28}$$

Substituting Eq. (26) with the elements of Eq. (25) results in Eq. (29):

$$x = -E^{-1}F - E^{-1}M^{T}\lambda \tag{29}$$

Since  $\Delta u$  is the control variable, Eq. (29) becomes Eq. (30):

$$\Delta u = \Delta u^o - E^{-1} M^T \lambda \tag{30}$$

In this case, the  $\Delta u^o = -E^{-1}F$  is the unconstrained optimal solution to the control signal, and  $-E^{-1}M^T\lambda$  is the correction factor based on the constraints computed by the HQP in case if  $\Delta u^o$  fails to meet the required constraints. To determine whether the optimal solution  $\Delta u^o$  is sufficient, it is substituted in Eq. (20), to obtain Eq. (31):

$$M\Delta u^o \le \gamma$$

(31)

If the above equation fails for any element of the constraint vectors, then the correction factor is computed using the HQP. The HQP technique is a numerical approach for solving the primal-dual problem. The primal-dual problem is equivalent to the following Eq. (32):

$$\max_{\lambda \ge 0} \min_{x} \left[ \frac{1}{2} x^{T} E x + x^{T} F + \lambda^{T} (M x - \gamma) \right]$$

(32)

Substituting Eq. (21) with the elements of Eq. (29) results in Eq. (33):

$$\max_{\lambda \ge 0} \left( -\frac{1}{2} \lambda^T P \lambda - \lambda^T K - \frac{1}{2} F^T E^{-1} F \right) \tag{33}$$

where

$$P = ME^{-1}M^T (34)$$

$$K = \gamma + ME^{-1}F = \gamma - M\Delta u^{o} \tag{35}$$

#### 2.4 Hildreth's quadratic programming technique

As discussed earlier, the  $\lambda$  is a vector of Lagrange multipliers. In Hildreth's quadratic programming (HQP), the  $\lambda$  is varied one element at a time. With a starting vector  $(\lambda^m)$ , a single element  $(\lambda_i^m)$  of the vector is modified, utilizing P and K to minimize the cost function (presented in Eq. (21)), which creates  $\lambda_i^{m+1}$ . In this case, if the modification requires  $\lambda_i^m < 0$ , then set  $\lambda_i^{m+1} = 0$ , rendering the constraint to be inactive. Then, the next element  $(\lambda_{i+1}^{m+1})$  of the vector is considered, and this process continues until all the elements of the entire  $\lambda^m$  vector are modified. This modification is computed using Eq. (36):

$$\lambda_i^{m+1} = \max(0, w_i) \tag{36}$$

where,

$$w_{i} = -\frac{1}{p_{ii}} \left[ k_{i} + \sum_{j=1}^{i-1} p_{ij} \lambda_{j}^{m+1} + \sum_{j=i+1}^{n} p_{ij} \lambda_{j}^{m} \right]$$

(37)

In this case,  $k_i$  and  $p_{ij}$  are the scalar *i*th and *ij*th elements of K and P, respectively. This is an iterative process, which continues either until the  $\lambda$  converges (so that  $\lambda^{m+1} \cong \lambda^m$ ) or until a maximum number of iterations is reached. This process concludes with a  $\lambda^*$  of either 0 or positive values. The positive values are the active constraints in the system at the time. The next step is to utilize  $\lambda^*$  in Eq. (3), to obtain our final control input as illustrated in Eq. (38):

$$\Delta u_{k+1} = \Delta u_{k+1}^{o} - E^{-1} M^{T} \lambda^{*} \tag{38}$$

## 2.5 Applying control signal

The control signal and the state signal are computed and updated using Eq. (6) (in Section 2.1). The first

element of  $\Delta U_k$  is used to update the control signal as shown in Eq. (39).

$$u_{k+1} = u_k + \Delta u_{k+1} \tag{39}$$

Next, the new control signal is used to determine the states for the next iteration, as presented in Eq. (40):

$$x_{k+1} = A_m x_k + B_m u_{k+1} (40)$$

In this case, the state of charge (SOC) (i.e.,  $x_{k+1}$ ,  $[0] = z_{k+1}$ ) is compared to reference values to determine if the Li-ion battery is fully charged. If the SOC is less than the reference values ( $z_{k+1}$  < reference), then the MPC algorithm is repeated to compute the next control signal.

## 3 Design approach and development platform

In this research work, we introduce our unique, novel, and efficient embedded architectures (two hardware versions and one software version) for the fast-charge model predictive controller (MPC). Our proposed embedded architectures for the fast-charge MPC algorithm are inspired by and based on the modified MPC algorithm for the lithium-ion battery cell-level MPC modeled by Trimboli's group [3, 4, 26]. We obtained the source codes written in Matlab for the existing fast-charge MPC algorithm from Trimboli's research group [4]. We use this validated Matlab model as the baseline for the performance and functionality comparison presented in Section 5.

For all our experiments, both software and hardware versions of various computations are implemented using a hierarchical platform-based design approach to facilitate component reuse at different levels of abstraction. Our designs consist of different abstraction levels, where higher-level functions utilize lower-level sub-functions and operators. The fundamental operators such as add, subtract, multiply, divide, compare, and square root are at the lowest level; the vector and matrix operations including matrix multiplication/addition/subtraction are at the next level; the four stages of the MPC, i.e., model generation, optimal solution, Hildreth's QP process, and state and plant generation, are at the third level of the design hierarchy; and the MPC is at the highest level.

All our hardware and software experiments are carried out on the ML605 FPGA development board [30], which utilizes a Xilinx Virtex 6 XC6VLX240T-FF1156 device. The development platform includes large on-chip logic resources (37,680 slices), MicroBlaze soft processors, and 2 MB on-chip BRAM (Block Random Access Memory) to store data/results.

All the hardware modules are designed in mixed VHDL and Verilog. They are executed on the FPGA (running at 100 MHz) to verify their correctness and performance. Xilinx ISE 14.7 and XPS 14.7 are used for

the hardware designs. ModelSim SE and Xilinx ISim 14.7 are used to verify the results and functionalities of the designs. Software modules are written in C and executed on the 32-bit RISC MicroBlaze soft processor (running at 100 MHz) on the same FPGA. The soft processor is built using the FPGA general-purpose logic. Unlike the hard processors such as the PowerPC, the soft processor must be synthesized and fit into the available gate arrays. Xilinx XPS 14.7 and SDK 14.7 are used to design and verify the software modules. The hardware modules for the fundamental operators are designed using single-precision floating-point units [31] from the Xilinx IP core library. The MicroBlaze is also configured to use single-precision floating-point units for the software modules. Conversely, the baseline Matlab model was designed using double-precision floating-point operators. This has caused some minor discrepancies in certain functionalities of the fast-charge MPC algorithm. These discrepancies are detailed in Section 5.

The speedup resulting from the use of hardware over software is computed using the following formula:

$$Speedup = \frac{BaselineExecutionTime(Software)}{ImprovedExecutionTime(Hardware)} \eqno(41)$$

## 3.1 System-level design

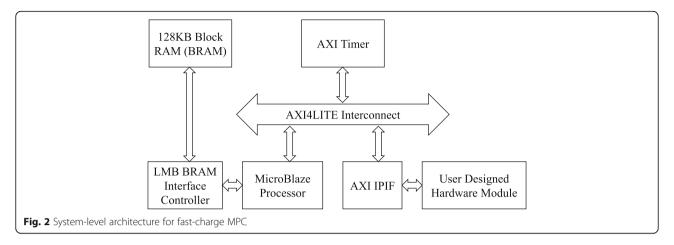

We introduce system-level architectures for our embedded hardware versions as well as our embedded software version. For some of the designs, we integrate on-chip BRAMs to store the input data needed to process the MPC algorithm and to store the final and intermediate results from the MPC algorithm. As shown in Fig. 2, the AXI (Advanced Extensible Interface) interconnect acts as the glue logic for the system.

We also incorporate MicroBlaze soft processor in both the hardware versions. For the embedded hardware, MicroBlaze is configured to have 128 KB of local on-chip memory. As illustrated in Fig. 2, our user-designed hardware module communicates with the MicroBlaze processor and with the other peripherals via AXI bus [32], through the AXI Intellectual Property Interface (IPIF) module, using a set of ports called the Intellectual Property Interconnect (IPIC). For the hardware designs, MicroBlaze processor is only employed to initiate the control cycle, to apply the control signals to the plant, and to determine the plant output signal. Conversely, the user-designed hardware module performs the whole fast-charge MPC algorithm. The execution times for the hardware as well as the software on MicroBlaze are

obtained using the AXI Timer [33] running at 100 MHz.

## 4 Embedded hardware and software architectures for MPC

In this section, we introduce unique, novel, and efficient embedded architectures (both hardware and software) for the fast-charge model predictive controller (MPC) algorithm. Apart from our main objective, one of our design goals is to create these embedded architectures to monitor and control not only one battery cell but also multiple battery cells individually, in a time-multiplexed fashion, in order to reduce the hardware resources required for BMS.

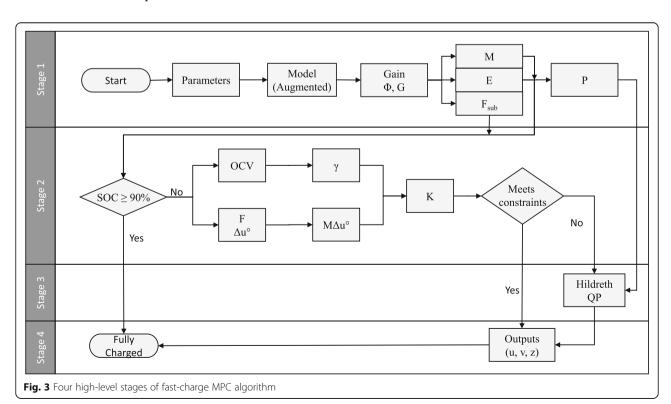

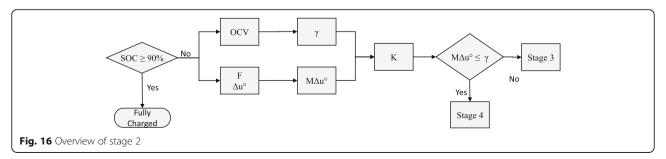

Initially, we investigate and analyze the functional flow of the MPC algorithm in [4], and then, we decompose the algorithm into four high-level stages (as shown in Fig. 3) to simplify the design process. The operations of the four consecutive stages are as follows:

- Stage 1—Compute the augmented model and gain (or data) matrices.

- Stage 2—Check the plant state (i.e., whether the charging is completed or not); compute the global optimal solution that is not subjected to constraints; determine whether the constraints are violated or not.

- Stage 3—Compute the new or adjusted solution using HQP procedure, if and only if, constraints are violated.

- Stage 4—Compute the new plant states and plant outputs. It should be noted that for experimental purposes, the plant output is computed in stage 4; however, in a real-world scenario, the plant output would be a measured value.

In order to enhance the performance and area efficiency of both our embedded hardware and software designs, all the time-invariant computations are relocated to stage 1 from other stages of the MPC algorithm. In this case, stage 1 is considered as the initial phase, which is performed only once at the beginning of the Control Prediction Cycle, whereas, subsequent stages (stages 2, 3, and 4) are performed in every sampling interval in an iterative fashion. Relocating the time-variant computations to stage 1 dramatically reduces the time taken to perform the subsequent stages and enhances the overall speedup of the MPC algorithm. For an example, consider the P parameter typically associated with stage 3. This P is created by multiplying a 32-word vector by a 32-word vector to create a  $32 \times 32$ matrix, which comprises 1024 multiplications. This computation would usually take 1032 clock cycles per iteration, if we employ a FPU multiplier, which produces a multiplication result every clock cycle, after an initial latency of 8 clock cycles. With the original fast-charge MPC algorithm [3], the P parameter is computed every time, when the stage 3 is executed. By moving the P parameter computation to stage 1, we save 1032 clock cycles per iteration. These execution times and speedups are detailed in Section 5.

There are two major advantages of using the modified fast-charge MPC algorithm for the embedded systems designs over other MPC algorithms in the existing literature:

- The fast-charge MPC algorithm contains only one matrix inversion, which is time-invariant, thus needing to be computed only once, provided that the temperature remains constant.

- The dual-mode approach allows for a short prediction horizon (N<sub>P</sub> = 10) and a short control horizon (N<sub>C</sub> = 1), which reduces the size of the matrices while maintaining the required stability. It also reduces the single matrix inversion to a scalar inversion, thus eliminating matrix inversion.

Our proposed embedded architectures for the fast-charge MPC are detailed in the following sub-sections.

#### 4.1 Embedded software architecture

Initially, we design and develop the software for the fast-charge MPC algorithm in C using the XCode integrated development environment. This software design is executed on a desktop computer with dual core i7

processor. Then, the results are compared and verified with the baseline results from the Matlab code. Both the C and Matlab results are also used to verify our results from the embedded software and hardware designs.

Due to the limited resources of the embedded devices, it is imperative to reduce the code size of the embedded software design. Hence, we dramatically modify the above software design (executed on desktop computer) to fit into the embedded microprocessor, i.e., MicroBlaze. In this case, we make the code leaner and simpler, in such a way that it fits into the program memory available with the embedded microprocessor, without affecting the basic structure and the functionalities of the algorithm. Many design decisions for hardware optimizations are also employed to optimize the embedded software design whenever possible, including reordering certain operations to reduce the redundancy (e.g., computing P parameter in stage 1). We also incorporate techniques to reduce the use of for loops appropriately and perform loop unrolling when the speed is important. Furthermore, we identify parts of the program, where offline computations can be done without exceeding the memory requirements.

The embedded software is designed to mimic the hardware. Apart from the usual computation modules, embedded software design consists of two sub-modules. One sub-module computes the temperature-dependent model parameters of resistances  $R_0$  and  $R_I$ , time constant  $\tau$ , and  $Q_{(charge)}$ , whereas the other sub-module computes the open circuit voltage (OCV) from the state of charge (SOC). The required parameters for the software design are computed from the measured data using a cubic spline technique. Since the empirical data are unlikely to change, the cubic spline data are computed offline with Matlab codes. The software flow for the fast-charge MPC is presented in Table 1.

**Table 1** Software algorithm for fast-charge MPC

| Stage | MPC software algorithm                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|-------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1.    | $ \begin{array}{l} \text{1.1. Get temperature} \\ \text{1.2. Call parameter function} \\ \text{1.3. Calculate } \Phi \text{ and G matrices} \\ \text{1.4. Create } G_{nf} \text{ and } G_{ff} \text{ (nf = near future and ff = far future) dual mode data)} \\ \text{1.5. Calculate E} \\ \text{1.6. Calculate P (matrix for Hildreth QP)} \\ \text{1.7. Build M (constraints vector)} \\ \text{1.8. Start loop - compare } x_m[0] \text{ (SOC) to reference to see if fully charged. If not fully charged, continue, else exit} \\ \end{array} $ |

| 2.    | 2.1. Calculate $F$<br>2.2. Solve ${}^{-}FE^{1}$ (optimal unconstrained $\Delta u$ from $J$ )<br>2.3. Build $\gamma$ (constraints vector)<br>2.4. Compare: $M\Delta u \leq \gamma$                                                                                                                                                                                                                                                                                                                                                                  |

| 3.    | 3.1. False – call Hildreth QP, develop new $\Delta \text{u}$ that meets constraints 3.2. True Goto Stage 4 (4.1)                                                                                                                                                                                                                                                                                                                                                                                                                                   |

4.1. Calculate the next control signal, next states, and outputs

4.2. Goto Start Loop (1.8)

#### 4.2 Embedded hardware designs

In this research work, we design and develop two hardware versions: the register-based hardware version 1 (HW\_v1) and the on-chip BRAM-based hardware version 2 (HW\_v2). With HW\_v1, a customized and parallel processing architecture is introduced to perform the matrix computations in parallel by mostly utilizing registers to store the data/results. By employing a parallel processing architecture, we anticipate an enhancement of the speedup of the overall MPC algorithm. With HW\_v2, an optimized architecture is introduced to address certain issues that have arisen with HW\_v1. By employing on-chip BRAMs to store the data/results, we expect a reduction in overall area, since the registers and the associated interconnects (in HW\_v1) typically occupy large space on chip. Conversely, the existing on-chip BRAMs are dual-port; hence, these could potentially hinder parallel processing of computations.

The register-based HW\_v1 is designed in such a way to follow the software functional flow of the MPC algorithm presented in Table 1, thus having similar characteristics as the embedded software design. In this case, the registers are used to hold the matrices, which is analogous to the indexing of the matrices in C programming. It should be noted that initially, we introduce HW\_v1, almost as a proof-of-concept work; next, we introduce HW\_v2 to address certain issues that have arisen with HW\_v1.

Xilinx offers two types of floating-point IP cores: AXI-based and non-AXI-based. For the register-based HW\_v1, we use the standard AXI-based IP cores for the fundamental operators. These IP cores provide standardized communications and buffering capabilities and occupy less area on chip, at the expense of higher latency. BRAM-based HW\_v2, we non-AXI-based IP cores for the fundamental operators. These IP cores allow the lowest latency adder (5-cycle latency) and multiplier (1-cycle latency) units to support 100 MHz system clock, at the expense of occupying more area on chip. The non-AXI-based cores have less stringent control and communication protocols; thus, proper timing of signals is required to obtain accurate results. With HW\_v2, we manage to use lower latency but more resource-intensive IP cores, since it consists of fewer multipliers and adders, whereas with HW\_v1, we have to use higher latency but less resource-intensive IP cores, since it comprises large number of multipliers and adders, due to the parallel processing nature of the design.

Initially, we design and develop the embedded hardware architectures for each stage as separate modules, analogous to our hierarchical platform-based design approach. The hardware designs for each stage consist of a data path and a control path. The control path manages the control signals of the data path as well as the BRAMs/registers. Next, we design a top-level module to integrate the four stages of the MPC algorithm and to provide necessary communication/control among the stages. Among various control/ communication signals, the top-level module ensures that the plant outputs, the state values, and the input control signals are routed to the correct stages at proper times. The control path of the top-level module consists of several finite-state machines (FSMs) and multiplexers to control the timing, routing, and internal architectures of the designs. The internal hardware architectures of the four stages of the MPC algorithm are detailed in the following sub-sections.

#### 4.2.1 Stage 1: augmented model and gain matrices

Stage 1, the initial phase of the MPC algorithm, is performed only once at the beginning of the Control Prediction Cycle. All the time-invariant computations, which are deemed independent of  $\chi_k$  and  $u_k$  are relocated and performed in stage 1, to ease the burden of the compute-intensive iterative portions of the MPC algorithm.

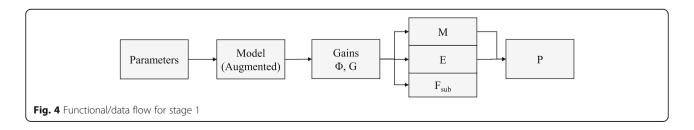

The general functional and data flow of stage 1 (for both HW\_v1 and HW\_v2) is depicted in Fig. 4. As illustrated, the relocated computations include E, M, P, and the sub-matrices for F. Stage 1 also consists of the augmented model and gain matrices for both the hardware versions and a parameter module only for HW\_v2. Initially, augmented model (in Fig. 4) is created from Eqs. (6), (7), and (8) depending on the temperature-dependent parameters, initial states  $x_k = [0, 0.5]$ , and initial control input  $u_k = 0$ .

**4.2.1.1 Computing parameters** Since varying temperatures are inevitable in the real-world scenario, for HW\_v2, we integrate an additional parameter module to compute the four temperature-dependent variables Q,  $R_0$ ,  $R_1$ , and r, utilized in the augmented model.

These variables are computed using a cubic spline interpolation of empirical data provided for Li-ion batteries. We use four cubic spline equations to compute the four variables. The general formula for a cubic spline interpolation is:  $y = a_3x^3 + a_2x^2 + a_1x + a_0$ , where x = T-ref; in this case, T is the temperature and ref is (min) from Table 2. As presented in Table 2, cubic spline approach uses six temperature regions. For HW\_v2, initially, the coefficients (i.e.,  $a_3$ ,  $a_2$ ,  $a_1$ , and  $a_0$ ) of the equations for all four variables are produced by Matlab codes and stored in a BRAM configured as a ROM. If the temperature varies, the base address of the temperature region in use (ref) is passed to the parameter module and the corresponding variables (parameters) are computed.

For HW\_v1, in stage 1, the parameter module is excluded due to the resource constraints on chip. In this case, for HW\_v1, the temperature-dependent parameters are considered as constants and stored in the registers, on the premise that the temperature will remain constant [4]. In this paper, for the experimental results and analysis (in Section 5), we consider the temperature to be constant for both hardware versions. With the current experimental setup, the additional parameter module does not impact the precision or the performance of the proposed embedded designs.

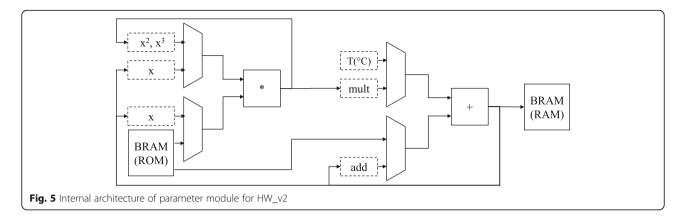

The internal architecture of the parameter module (from Fig. 4) for HW\_v2 is depicted in Fig. 5. This module executes a cubic equation for each of the temperature-dependent variables. The regions contain different coefficients based on empirical data. As illustrated in Fig. 5, these coefficients are stored in ROM, and the region defines the memory location of the coefficients and the reference values. To execute the cubic equation, the parameter module uses an 8-cycle multiplier, 12-cycle adder, and multiplexers. There are four cubic equations, one for each parameter. This module initially computes the x term for all four equations and then adds the constants. Next, the  $x^2$  term is calculated and multiplied by the four corresponding coefficients, and the resulting value is added to the previous terms. This is repeated for the  $x^3$  term. This multiply-add approach is timed in such a way to eliminate the need for extra registers to hold the values. Once the add

Table 2 Temperature regions for cubic spline

| Region | Range                    | Reference (°C)  |

|--------|--------------------------|-----------------|

| 1      | -15 °C ≤ T < -5 °C       | <del>- 15</del> |

| 2      | -5 °C ≤ T < 5 °C         | <b>-</b> 5      |

| 3      | 5 °C ≤ <i>T</i> < 15 °C  | 5               |

| 4      | 15 °C ≤ <i>T</i> < 25 °C | 15              |

| 5      | 25 °C ≤ <i>T</i> < 35 °C | 25              |

| 6      | 35 °C ≤ T                | 35              |

completes, the next multiply is ready to be added to the total.

**4.2.1.2** Creating augmented model After computing the parameters, we design and develop the matrices of the augmented model. The elements of the modified fast-charge MPC state-space equations (i.e., Eqs. (1)–(8) [4]) are presented below in (42).

$$A_{m} = \begin{bmatrix} 1 & 0 \\ 0 & e^{-\Delta t}/R_{1}C_{1} \end{bmatrix},$$

$$B_{m} = \begin{bmatrix} -\frac{\eta \Delta t}{Q} \\ R_{1} \left(1 - e^{-\Delta t}/R_{1}C_{1}\right) \end{bmatrix} \text{ and}$$

$$x_{m,k} = \begin{bmatrix} z_{k} \\ v_{c_{1},k} \end{bmatrix}$$

$$(42)$$

The augmented state-space equation matrices are given in Eq. (9) (in Section 2.1), where,  $\Delta t$  is the sampling time (considered as 1 s) and  $\eta$  is the cell efficiency (considered as 0.997). Also, the  $e^{-\Delta t/\tau}$  term is currently stored as a constant and an input for both the hardware versions. For both HW\_v1 and HW\_v2, the augmented model computes all the elements in Eq. (42) and then stores the values in the correct order of the matrices, in registers (for HW\_v1) and in BRAMs (for HW\_v2). In addition, the augmented model for HW\_v2 computes  $P_I$  and  $P_2$  in Eq. (24).

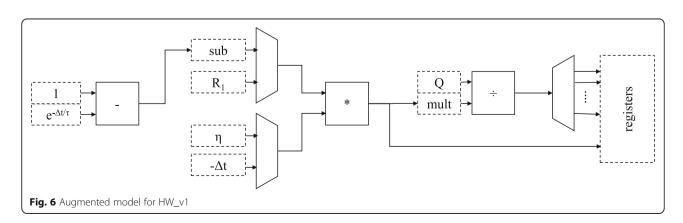

The internal architecture of the augmented model for HW\_v1 is shown in Fig. 6. In order to compute the values in Eq. (42) for the augmented model, a subtraction FPU, multiplication FPU, a division FPU, and three multiplexers are required. The results are stored in registers to be forwarded directly to the subsequent modules.

**4.2.1.3 Computing gain matrices** Next, we perform the gain matrix computations including the  $\Phi$ ,  $G_{rf}$  and  $G_{ff}$ . Each gain matrix has identical computations, which are independent of each other. In our design, the  $\Phi$  and G matrices are developed for both the terminal voltage  $\nu_k$  and SOC  $Z_k$  separately, resulting in  $\Phi_{\nu}$ ,  $\Phi_z$ ,  $G_{\nu}$ , and  $G_z$ . The gain matrices are derived from Eq. (12), where  $\Phi_{\nu}$  and  $\Phi_z$  are:

$$\Phi_{\nu} = \begin{bmatrix}

\tilde{C}_{\nu} \\

\tilde{C}_{\nu}\tilde{A} \\

\tilde{C}_{\nu}\tilde{A}^{2} \\

\tilde{C}_{\nu}\tilde{A}^{N_{p}-1}

\end{bmatrix} \text{ and } \Phi_{z} = \begin{bmatrix}

\tilde{C}_{z} \\

\tilde{C}_{z}\tilde{A} \\

C_{z}\tilde{A}^{2} \\

\tilde{C}_{z}\tilde{A}^{N_{p}-1}

\end{bmatrix}$$

(43)

It should be noted that in our design, from Eq. (9), the  $\tilde{B}$  is considered as  $\begin{bmatrix} 0 & 0 & 1 \end{bmatrix}^T$ ; thus, each column

of G is derived from the third column of  $\Phi$ . This only requires arranging the elements of the G matrix in registers or BRAMs, instead of re-computing these elements. In this case,  $G_{rf}$  is a  $N_P \times N_C$  matrix and  $G_{ff}$  is a  $N_P \times N_P - N_C$  matrix. As in Eq. (44), for  $N_c = 1$ ,  $G_{rf}$  is the first column of G, from Eq. (12), and  $G_{ff}$  comprises the rest of the columns. Utilizing  $\tilde{C}_{\nu}$  and  $\tilde{C}_z$ , which incorporated the feed-through term from Eq. (44), we create  $G_{rf,\nu}$   $G_{ff,\nu}$   $G_{nfz}$ , and  $G_{ffz}$ .

$$G = \begin{bmatrix} \tilde{C}\tilde{B} \\ \tilde{C}\tilde{A}\tilde{B} \\ \tilde{C}\tilde{A}^{2}\tilde{B} \\ \vdots \\ \tilde{C}\tilde{A}^{N_{p}-1}\tilde{B} \end{bmatrix}_{G_{ff}} \begin{bmatrix} 0 & 0 & \cdots & 0 \\ \tilde{C}\tilde{B} & 0 & \cdots & 0 \\ \tilde{C}\tilde{A}\tilde{B} & \tilde{C}\tilde{B} & \cdots & 0 \\ \tilde{C}\tilde{A}\tilde{B} & \tilde{C}\tilde{B} & \cdots & \tilde{C}\tilde{A}^{N_{p}-N_{c}}\tilde{B} \end{bmatrix}_{G_{ff}}$$

$$(44)$$

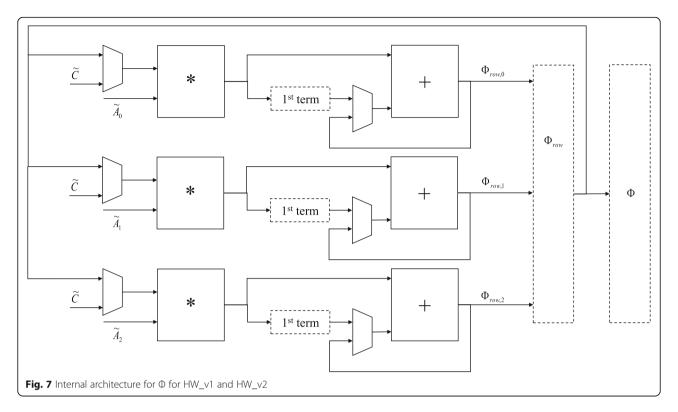

The internal architecture for computing the  $\Phi$  matrix (for both HW\_v1 and HW\_v2) is shown in Fig. 7. The size of  $\Phi$  is determined by the prediction horizon  $(N_p)$ , the number of states,  $(N_s)$ , and the number of inputs,  $(N_{in})$ , and is an  $N_p x$   $(N_s + N_{in})$  matrix. As illustrated, the  $\Phi$  includes three multiply-and-accumulate units to compute three elements of each row in parallel. Instead of adding a zero (0) to the first term, as in a typical multiply-and-accumulate unit, in this case, the first term

is placed in a register until the second term is ready for the add operation. After the addition of the first two terms, the rest of the terms are subjected to multiply-and-accumulate operation. As shown in Fig. 7, the internal architecture also comprises a feedback-loop unit, which determines the appropriate values to be loaded in each iteration. In this case, each subsequent row of  $\Phi$  is the previous row multiplied by  $\tilde{A}$ . Our design comprises three multiply-and-accumulate (MAC) units that compute each column of  $\tilde{A}$  (as shown in Fig. 8) in parallel.

As demonstrated in Fig. 7, both hardware versions have the same internal architecture for computing the  $\Phi$  matrix. In this case, HW\_v1 waits until  $\Phi$  matrix computation is completed and then loads  $G_{rf}$  and  $G_{ff}$ . Also, HW\_v1 employs two gain matrix modules to compute  $\left[\Phi_{v},\ G_{nfv},\ G_{ffv}\right]$  and  $\left[\Phi_{z},\ G_{nfz},\ G_{ffz}\right]$  matrices in parallel.

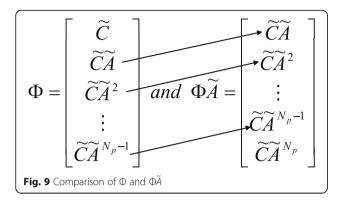

Conversely, HW\_v2 computes each row of the  $\Phi$  matrix and then saves the row term in an appropriate memory location, in order to subsequently build  $\Phi$ ,  $G_{rf}$ , and  $G_{ff}$  utilizing an addressing algorithm. Furthermore, HW\_v2 computes and saves the  $\Phi_v \tilde{A}$  and  $\Phi_z \tilde{A}$  matrices. As illustrated in Fig. 9, the calculation of  $\Phi$  and  $\Phi \tilde{A}$  only differs by one row. Hence, by merely computing one

additional row,  $\Phi \tilde{A}$  can be built in the same fashion and at the same time as  $\Phi$ ,  $G_{rf}$ , and  $G_{ff}$ , using one extra iteration.

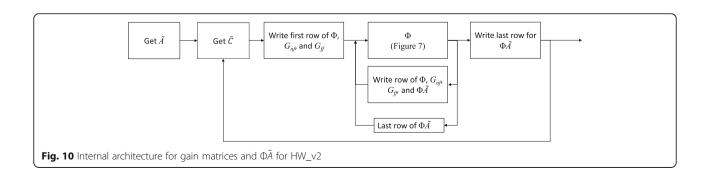

Unlike HW\_v1, HW\_v2 computes the  $\left[\Phi_{\nu},\ G_{n\!f\!\nu},\ G_{f\!f\!\nu},\ \Phi_{\nu}\tilde{A}\ \right]$  and  $\left[\Phi_{z},\ G_{n\!f\!z},\ G_{f\!f\!z},\ \Phi_{z}\tilde{A}\ \right]$  sequentially. The functional architecture of the gain matrices for HW\_v2 is depicted in Fig. 10. In this case, the hardware module for computing the  $\Phi$  matrix (from Fig. 7) is reused in this module.

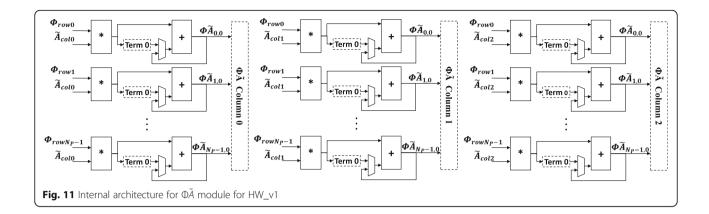

HW\_v1 computes  $\Phi \tilde{A}$  in a separate module (as in Fig. 11), after completing the  $\Phi$  matrix computation. In this case, we employ 10 MAC units to compute all the elements in each column of  $\Phi \tilde{A}$  in parallel. As illustrated in Fig. 11, the columns are computed sequentially. Also, HW\_v1 employs two  $\Phi \tilde{A}$  modules to compute  $\Phi_{\nu} \tilde{A}$  and  $\Phi_{z} \tilde{A}$  in parallel.

**4.2.1.4 Time-invariant computations for HW\_v1** As mentioned in Section 4.2.1, all the time-invariant computations (E, M, P, and sub-matrices of F), which are deemed independent of  $\chi_k$  or  $u_k$  (from stages 2 and 3), are relocated to stage 1, thus significantly reducing the computation burden in other stages. For HW\_v1 and HW\_v2, these computations are designed using different techniques. For register-based HW\_v1, we employ parallel processing architecture, whereas BRAM-based HW\_v2 is executed in pipeline fashion.

## E module for HW\_v1

First, we present the architecture for HW\_v1, since it intuitively follows the order of operations. Considering Eq. (24) from Section 2.3, there are no  $\chi$  or  $\Delta u$  terms, unless the temperature varies. As a result, E remains constant and can be performed in stage 1. We decompose this E computation into several

$$\left[\begin{array}{c|c} \Phi_{row} & \right] \left[ \widetilde{A}_0 & \widetilde{A}_1 & \widetilde{A}_2 \\ & & \end{array} \right] = \left[ \Phi_{row\_next} \right]$$

Fig. 8 Organization of  $\Phi \tilde{A}$

sub-functions, in such a way that each sub-function comprises only one matrix computation. Then, for  $HW_v1$ , we design separate sub-modules to perform different matrix computations such as a vector-scalar multiplication (VS), a vector-vector multiplication (VV), a vector-matrix multiplication (VM), and a vector-matrix transpose multiplication (V $^TM^T$ ). The decomposed computations are presented in Eqs. (45)–(53):

$$E_1 = G_{nfz}^T G_{nfz} \tag{45}$$

$$E_2 = E_{2a}\mathbf{m}, \quad E_{2a} = G_{nfz}^T G_{ffz} \tag{46}$$

$$E_3 = E_{3a}G_{nfz}, \ E_{3a} = \mathbf{m}^{\mathrm{T}}G_{ffz}^T$$

(47)

$$E_4 = E_{4a}\mathbf{m}, \ E_{4a} = E_{3a}G_{ffz}$$

(48)

$$E_5 = E_{5a}P_2, \quad E_{5a} = \mathbf{m}^{\mathsf{T}}\mathbf{m} \tag{49}$$

$$P_1 = rw(1 - \gamma_p) \tag{50}$$

$$P_2 = rw\gamma_{\scriptscriptstyle D} \tag{51}$$

$$E = E_1 + P_1 + E_2 + E_3 + E_4 + E_5 \tag{52}$$

$$Einv = E^{-1} \tag{53}$$

In this case, the control horizon is  $N_c = 1$ , and E and the inverse of E are scalars, which significantly reduces the complexity of the MPC algorithm. Since division and inversion floating-point operations typically incur the

highest latency, by computing the  $E^{-1}$  in stage 1, the subsequent stages mostly comprise multiplication operations with much lower latency (1 to 8 cycles based on the FPU). For HW\_v1, the final internal architecture for E module is derived from Eq. (25) from Section 2.3. From Eq. (25), it is observed that the last term is in fact  $(E_2 + E_4 + E_5)u_k$ . In this case, integrating Eq. (54) to the E module reduces the number of outputs  $F_{3a}$ , i.e., from three 32-bit values to a single 32-bit value.

$$F_{3a} = E_2 + E_4 + E_5 \tag{54}$$

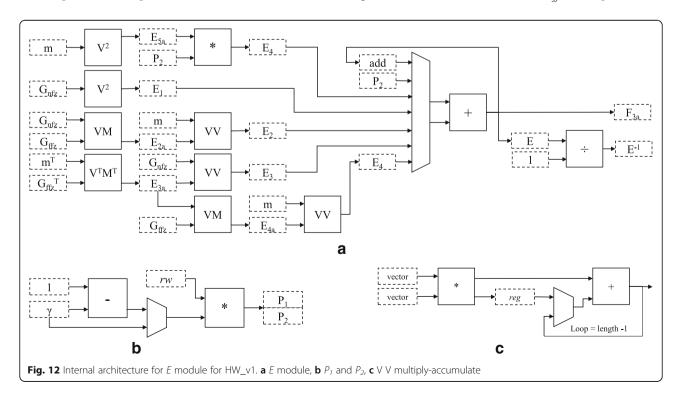

As illustrated in Fig. 12a, the E module for HW\_v1 computes the Eqs. (45)–(54). As shown, the E module for HW v1 comprises several sub-modules to compute various vector and matrix operations. These sub-modules utilize MAC units (Fig. 12c) to perform the necessary vector/matrix operations. Our MAC unit is designed in such a way to reduce each final MAC result by 12 clock cycles. In our designs, the vector-vector multiplication (VV) is identical to vector squared  $(V^2)$  except the former accepts two separate vectors, whereas the latter accepts only one; vector-matrix multiplication (VM) and vector-matrix transpose multiplication  $(V^TM^T)$  are also identical, except the former uses the number of columns of the matrix to determine the number of processing elements (PEs), whereas the latter uses the number of rows of the matrix to determine the number of PEs. Furthermore, as depicted in Fig. 12b, we design a separate sub-module to compute the tuning parameters  $P_1$  and  $P_2$ , which is executed in parallel with the *E* module. This significantly reduces the control logic required for the *E* module.

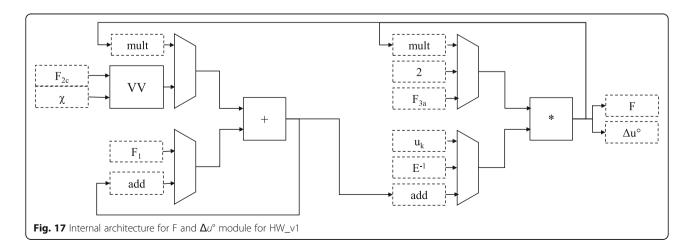

## F\_sub module for HW\_v1

We design the F\_sub module to compute the sub-matrices for F. This module computes all the F terms, presented in Eqs. (55)–(58), which are derived from Eq. (25).

$$F_{1a} = G_{nfz}^T + E_{3a} \tag{55}$$

$$F_1 = F_{1a}R_s \tag{56}$$

$$F_{2a} = F_{1a}\Phi_z \tag{57}$$

$$F_{2c} = F_{2a}\tilde{A} \tag{58}$$

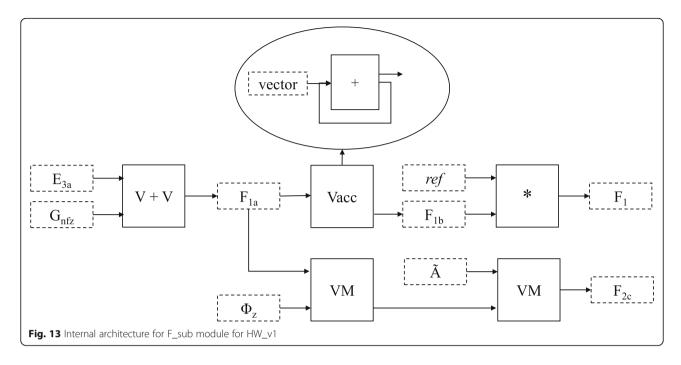

The internal architecture of the F\_sub module is depicted in Fig. 13, which consists of a vector-addition module (V+V), a vector-accumulation module (VAcc), two VM modules, and a FPU multiplier. In this case, the former two sub-modules (V+V) and VAcc) utilize FPU adders to perform the required operations.

## M module for HW\_v1

We also design the M module to compute M constraints. The M and  $\gamma$  are presented in Eq. (26). All the elements of M and some elements of  $\gamma$  can be computed with Eqs. (59)–(65) as follows:

$$Mposv_a = G_{ffv}\mathbf{m} \tag{59}$$

$$Mposz_a = G_{ffz}\mathbf{m} \tag{60}$$

$$Mposv = (G_{nfv} + Mposv_a) (61)$$

$$Mnegv = -Mposv$$

(62)

$$Mposz = (G_{nfz} + Mposz_a) (63)$$

$$\Phi A \nu = \Phi_{\nu} \tilde{A} \tag{64}$$

$$\Phi Az = \Phi_z \tilde{A} \tag{65}$$

HW\_v1 employs separate modules to perform  $G_{ff}$ **m** and  $\Phi \tilde{A}$ . The internal architecture for  $\Phi \tilde{A}$  is demonstrated in Fig. 11, and the architecture of  $G_{ff}$ **m** computation is

similar to the **VM** sub-module. With the M module, the negation operations (in Eqs. (61) and (63)) are performed by reversing the most significant bit (MSB) of the 32-bit floating-point values, thus reducing the logic utilized for these operations.

## P module for HW v1

Next, we design the P module for HW\_v1, which is derived from Eq. (34),  $P = ME^{-1}M^{T}$ . As discussed in Section 2.4, Hildreth's quadratic programming (HQP) utilizes this equation to compute  $\lambda$  vector. We decompose this equation to Eqs. (66) and (67) as follows:

$$M_{conEinv} = ME^{-1} (66)$$

where, Eq. (67) performs a vector-scalar multiplication.

$$P = M_{conEinv}M^{T} (67)$$

In this case, P is a square symmetric matrix; hence, the number of columns and rows are equal to the length of M (in our case 32). To compute this matrix, we use an efficient computation assignment algorithm developed by our group [34]. Utilizing this algorithm, elements of P matrix are executed in parallel using several parallel PEs. In this case, n number of PEs process n number of elements (of the matrix) at a time and computes the whole P matrix with no idle time.

Due to the size of the P matrix (32 × 32), registers are not suitable to store the matrix on chip. Our attempt to store the matrix using registers caused our initial design to exceed the chip resources by 25%. Therefore, we integrate BRAM to the P module to store the P matrix in

HW\_v1. In this case, we use only two PEs to compute elements of the *P* matrix, due to the port limitations of the BRAMs. The PEs consist of a multiplier and logic elements to ensure that the inputs to the multiplier are ready every clock cycle to reduce the latency. The results of *P* matrix computation are reused in stage 3.

In summary, HW\_v1 is designed with separate modules, including **GFFm**,  $\Phi A$ , **E**, **F\_sub**, **M**, and **P**, to execute various computations in stage 1. In this case, two **GFFm** modules compute Eqs. (59) and (60) in parallel, and two  $\Phi A$  modules compute Eqs. (64) and (65) in parallel. The **F\_sub** module computes Eqs. (55)–(58), the **M** module computes Eqs. (61)–(63), and finally **P** module computes Eqs. (66) and (67).

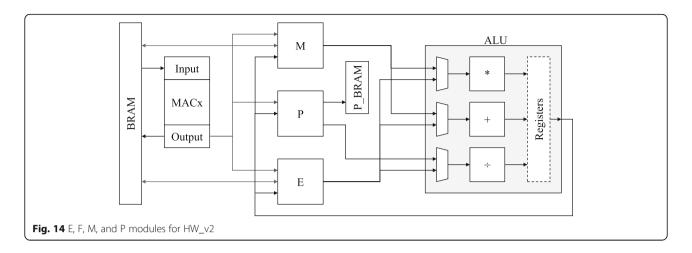

**4.2.1.5** Time-invariant computations for HW\_v2 For the internal architecture for HW\_v2, we use a novel and unique approach to perform the *E*, *F*, *M*, and *P* computations. In this case, we design a unique pipelined multiply-and-accumulator (MACx) module to perform various vector and matrix multiplication operations in sequence. The MACx has a wrapper, which handles reading/writing from/to the BRAMs during the vector/matrix operations.

For HW\_v2, the matrix addition and the scalar operations are typically performed in the **E**, **M**, and **P** modules. In this case, the **E** module organizes the scalar addition, multiplication, and division necessary to generate  $E^{-1}$ . The **M** module performs the scalar addition and multiplication to generate M (for Eqs. (61)–(63)) and  $F_{Ia}$  (for Eq. (55)), when using BRAMs to store the vectors. The Eqs. (61) and (55) would generate the same values.

Figure 14 shows the top-level architecture for HW\_v2 for the time-invariant computations *E*, *F*, *M*, and *P*. As illustrated, the multiplier, adder, and divider FPUs are shared among the **E**, **M**, and **P** modules, and multiplexers are utilized to control the routing and internal architecture of these modules. The outputs of these FPUs are forwarded to the **E**, **M**, and **P** modules, and the final results are stored in the BRAMs.

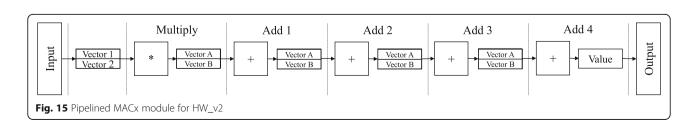

The internal architecture of the pipelined MACx module is depicted in Fig. 15. The MACx is primarily designed to perform vector multiplications. The input module of the MACx decomposes the matrix computations into vector operations. The pipelined MACx (for HW\_v2) executes the vector operations (for three or more vectors) faster than its parallel HW\_v1 counterpart. In this case, we carefully configure the FPUs to have the lowest latency without compromising the highest system-clock frequency (100 MHz). For HW\_v2, the FPUs for the multiplier and the adder have 1-cycle and 5-cycle latencies, respectively, whereas for HW\_v1, the FPUs for the multiplier and the adder have 8-cycle and 12-cycle latencies, respectively. However, there is a trade-off; low-latency IP cores occupy more area on chip. This might not be an issue for the BRAM-based HW\_v2, since the overall design occupies less area on chip compared to the register-based HW\_v1. This is not only because HW\_v2 employs BRAMs instead of registers to store the data/results, but also it utilizes far less IP cores than HW\_v1.

Furthermore, in HW\_v1, computations such as  $G_{ffz}m$  are not available for subsequent operations until the whole computation has been completed (i.e., all the elements are computed). Conversely, in HW\_v2, after one element is computed in one operation, that element can be used in subsequent operations. For instance, for HW\_v2, when MACx completes the first vector computation (i.e.,  $G_{ffz\_row0} * m$ ), the resulting element and the first element of  $G_{nfz}$  in Eq. (63) is utilized by the M module to generate the first element of Mposz. This dramatically reduces the time required to execute stage 1, as detailed in Section 5.

With the pipelined MACx, the input wrapper controls the order of the operations (i.e., execution order). Since the computations are performed sequentially, the "execution order" is determined carefully, to minimize the wait or stall time for dependent operations and to optimize the utilization of the limited memory ports. The two performance bottlenecks of stage 1 (for HW\_v2) are the limited memory ports and the IP core latency. The design uses three types of BRAM memory: a dual port ROM that stores constants, a single-port RAM-low, and a dual-port RAM-high. The input wrapper has access to a single read port in each of the memories. The ports are reserved only when the vectors are being fetched from the memory and freed once the data are loaded into the MACx input buffers. The execution order using the pipelined MACx for HW\_v2 is as follows:

- 1.  $E_{5a} = \mathbf{m}^T \mathbf{m}$ , Eq. (49). In this case, a single ROM port is utilized to preload the m vector into both input buffers of the MACx. This occurs in parallel with the  $\Phi$  and the gain matrix calculations. After the multiply and add operations of the MACx are completed, the output MACx module sends a signal to the E module, indicating that this value is ready. The E module accesses the value from the MACx output register and multiplies this value with  $P_2$  to create  $E_5$ . The MACx output register is also the input register used to store the data in RAM-high. This value is stored in the memory while the E module accesses the value to send it to an adder.

- 2.  $E_{3a} = \mathbf{m}^T G_{ffz}^T = G_{ffz} \mathbf{m} = Mposz_a$ , Eq. (47). From step 1, the m vector is already loaded into one input buffer of the MACx, and single RAM-low port is required to load a row of  $G_{ffz}$  into the other input buffer of MACx. The multiplier sends a signal to the input module to preload the next row of  $G_{ffz}$ into the MACx input register. The m vector remains in the input buffer until cleared or overwritten. This step continues until all the rows of  $G_{ffz}$ have been entered. Once the required vector is available, the output MACx module sends a signal to the M and input modules and then loads the vector into RAM-high. The M module uses this vector  $(E_{3a})$  to create  $F_{1a}$ .  $E_{3a}$  is also used in step 5 to create  $E_3$ . Next, steps 3 and 4 are selected to be executed, since inputs to these steps are already available. Furthermore, these two steps can be executed in the pipeline with no stall states.

- 3.  $E_1 = G_{nfz}^T G_{nfz}$ , Eq. (45). Since  $G_{nfz}$  is a vector, a single RAM port is required to load  $G_{nfz}$  into both MACx input buffers. After completing this computation, the output MACx module sends a signal to the E module, indicating that this value is ready. The E module adds this value ( $E_I$ ) to  $E_5$  and stores it in a temporary register.

- 4.  $E_{2a} = G_{nfz}^T G_{ffz}$ , Eq. (46). From step 3,  $G_{nfz}$  is already loaded into the MACx input buffer and a single RAM port is used to pre-fetch the columns of  $G_{ffz}$ . Once the multiplier indicates that it starts executing, the input module preloads the next column of  $G_{ffz}$  into the input buffer to compute the next term of  $E_{2a}$ . This step continues for all the columns of  $G_{ffz}$ .  $E_{2a}$  is used in step 6 to create  $E_2$ . As a result,  $E_{2a}$  is stored in RAM-low, and a signal is forwarded to the input module once it is completed.

- 5.  $E_3 = E_{4a} = E_{3a}G_{ffz}$ , Eq. (48). The time it takes to load steps 3 and 4 ensures that the operation started in step 2 ( $E_{3a}$ ) is completed. The input module ensures that this value is ready by checking the complete signal. One port from each RAM is used to preload  $E_{3a}$ , while a column of  $G_{ffz}$  is loaded into the MACx

- input buffers. This step continues until all the columns of  $G_{f\!f\!z}$  have been loaded. Upon completion of the MACx operations, the output module sends a signal to the E module indicating that the value ( $E_3$ ) is available. The E module accesses the MACx output register to add this value to  $E_5 + E_1$ .

- 6.  $E_2 = E_{2a}$ **m**, Eq. (46). The m vector is loaded into one MACx input buffer using a ROM port. Simultaneously,  $E_{2a}$  is completed, and step 5 is being executed. Then,  $E_{2a}$  is loaded into the other input buffer using a RAM-low port. Once the MACx operation is completed, the output module sends a signal to the E module and the E module accesses the MACx output register to add this value to  $E_5 + E_1 + E_3$ .

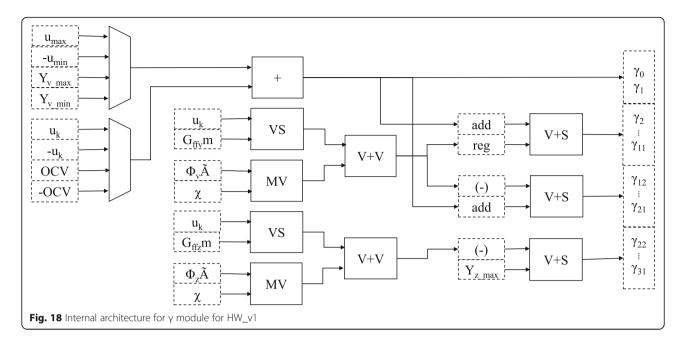

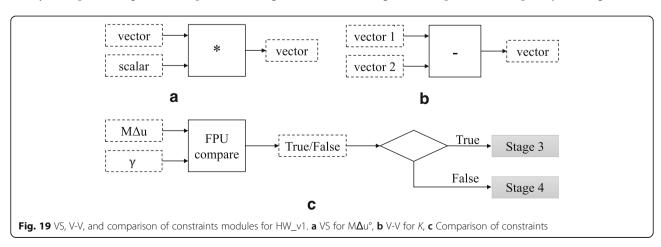

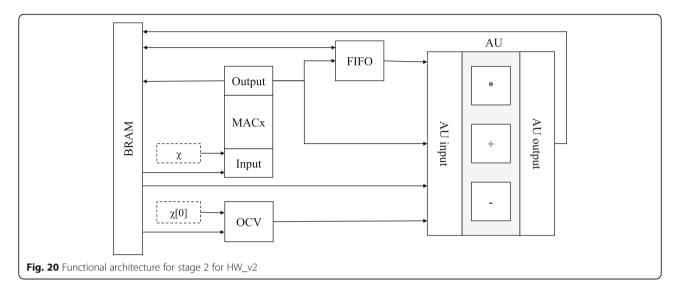

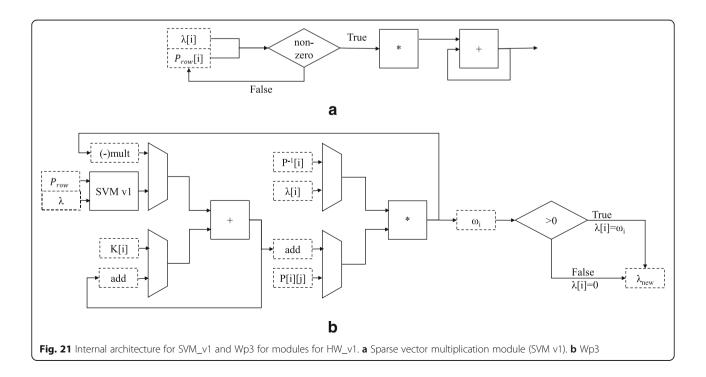

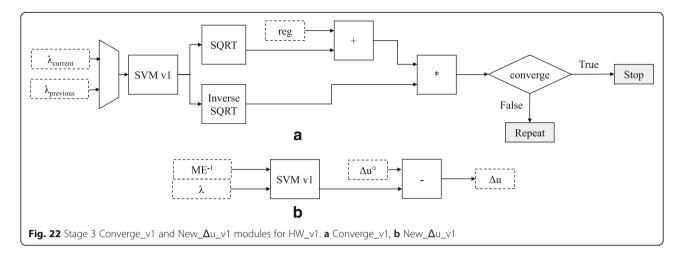

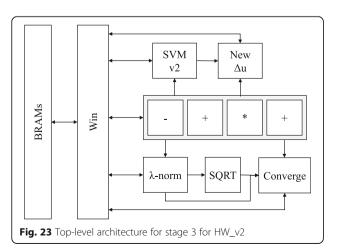

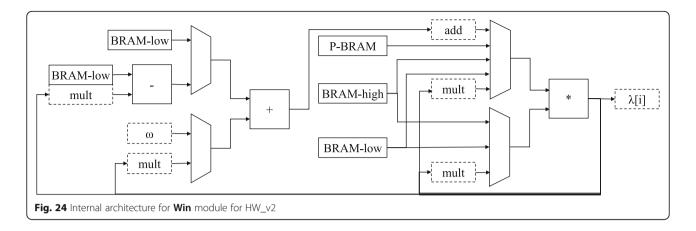

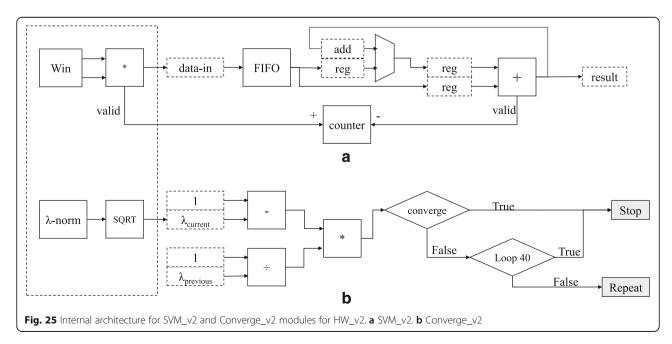

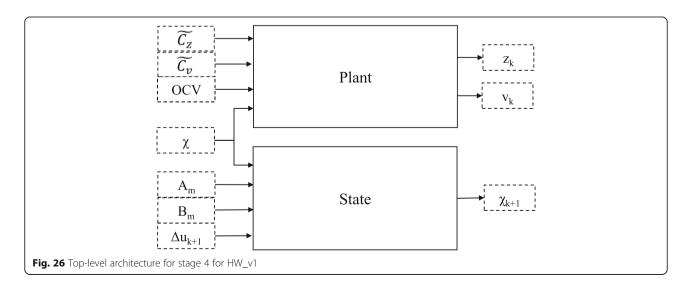

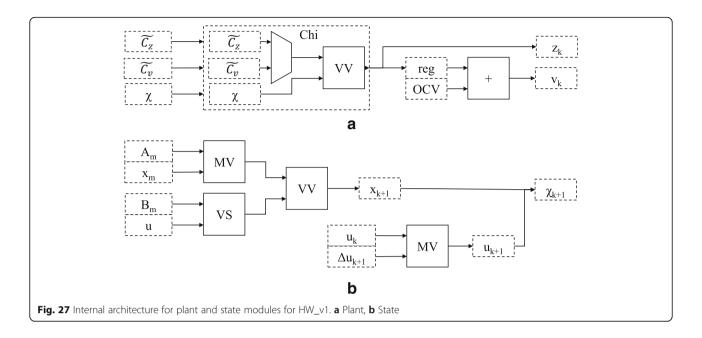

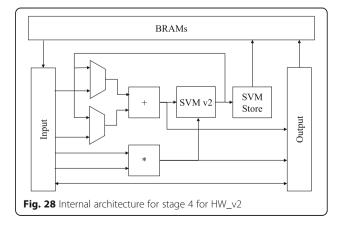

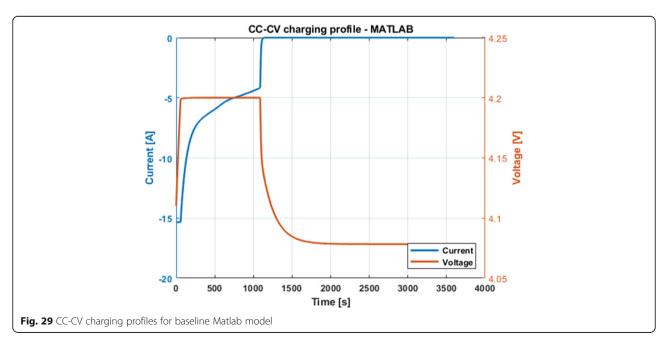

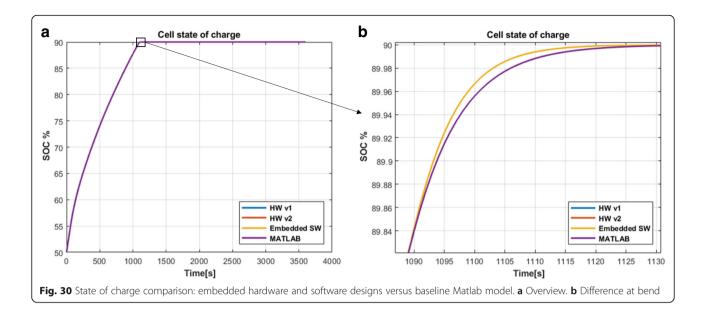

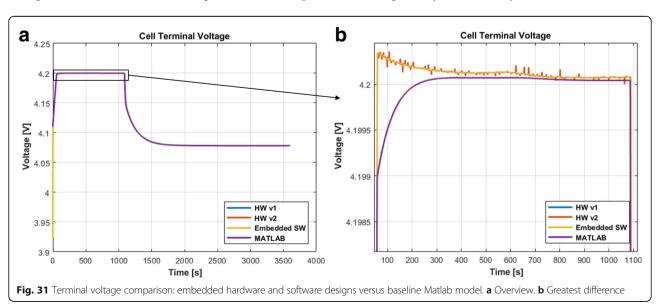

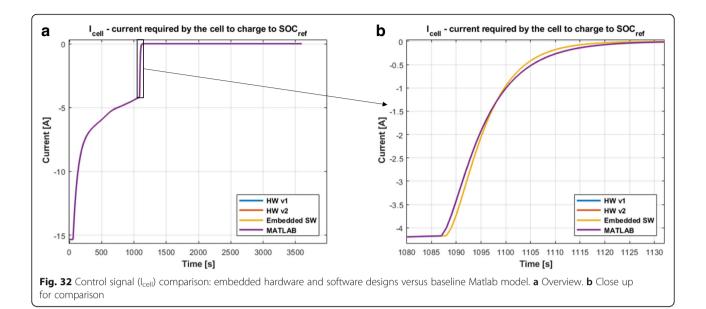

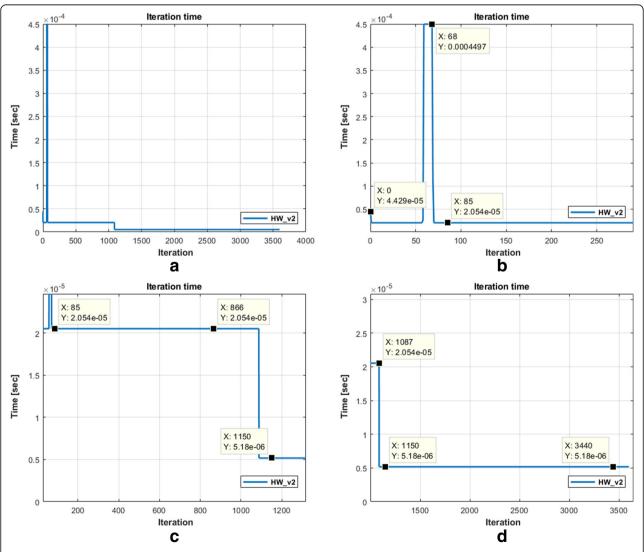

- 7.  $Mposv_a = G_{ffv}\mathbf{m}$ , Eq. (59). As mentioned before, the m vector is already present in the input buffer of the MACx. Hence, a RAM port is required to load the rows of  $G_{ffv}$  into the other MACx input buffer. This step continues until all the rows of  $G_{ffv}$  have been operated on. Once the MACx operations are completed, the output module sends a signal to the M module. The M module uses this value to build the M constraint vector.