RESEARCH Open Access

# A low cost and fast controller architecture for multimedia data storage and retrieval to flash-based storage device

Samiran Banerjee\* and Sumitra Mukhopadhyay

### **Abstract**

Real-time multimedia data access plays an important role in electronic systems; as time goes by, with decrease in data processing speed and increase in communication time, storage time, and retrieval time, the overall response time increases for real-time applications. Therefore, in this paper, a novel real-time, fast, low-cost, system-on-chip (SoC) controller has been proposed and implemented where large volume of data can be efficiently stored and retrieved from flash memory cards. It is being implemented only using hardware description language (HDL) on a field programmable gate array (FPGA) chip without using any other on-board or external hardware resources or high-level languages. The entire controller architecture, in a single chip, contains five different modules and is designed using finite state machine (FSM)-based approach. The modules are card initialization module (CINM), idle module (IM), card read module (CRM), card write module (CWM), and decision module (DM). The architecture is completely synthesized for Spartan 3E xc3s500e-4-fg320 FPGA with only 5% of the total logic utilization. The experimental results tested for microSD, SD, and SDHC cards of different size, and these show that the architecture uses less hardware and clock cycles for card initialization and single/multiblock read/write procedure.

**Keywords:** Flash memory read/write, Secure Digital High Capacity (SDHC) card, MicroSD card, Serial peripheral interface (SPI), Finite state machine (FSM), Very high speed integrated circuit hardware description language (VHDL), Field programmable gate array (FPGA)

### 1 Introduction

The flash-based memory storage device, introduced by Toshiba in 1984, is basically a non-volatile electronic memory and used whenever a shock resistance is the key requirement of any application [1]. The Secured Digital High Capacity (SDHC) card, for example, is a flash-based memory storage device and is mainly designed to meet certain requirements such as security, capacity, performance, and environmental issues inherent in newly emerging audio and video consumer electronic devices. The Secured Digital (SD) card standard is designed and licensed by SD Card Association [2] and is a collaborative effort of the three manufacturers, namely Toshiba, SanDisk, and MEI [3].

\*Correspondence: samiranbanerjee1991@gmail.com Institute of Radio Physics and Electronics, University of Calcutta, 92, APC Road, Kolkata, India The SD card includes an on-card intelligent controller to manage the interface protocol, security algorithms, data storage and retrieval, error handling and corresponding error correction code (ECC) algorithms, defect handling and diagnostics, power management, and clock control [1]. However, to interface the SDHC card (slave unit) with master unit (e.g., computer, host, or any application-specific device), we need a system which can talk with the on-card controller of the SDHC card for smooth execution of single/multiblock data read/write.

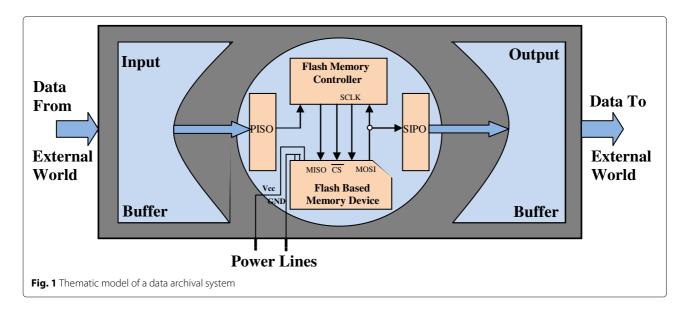

Figure 1 represents a generic model of a data archival system and it shows how the flash-based cards like microSD, SD, or SDHC cards can be used as the plug and play memory module for real-time application. Generally, the signal is received from the external world in a buffer, converted into a serial bit stream and subsequently stored into the memory card. The stored data at later stage may be transmitted for further processing. Also, the flash memory acts as a portable unit and it can be

removed from the system where it is presently housed in and accessed by some other system to retrieve the desired signal.

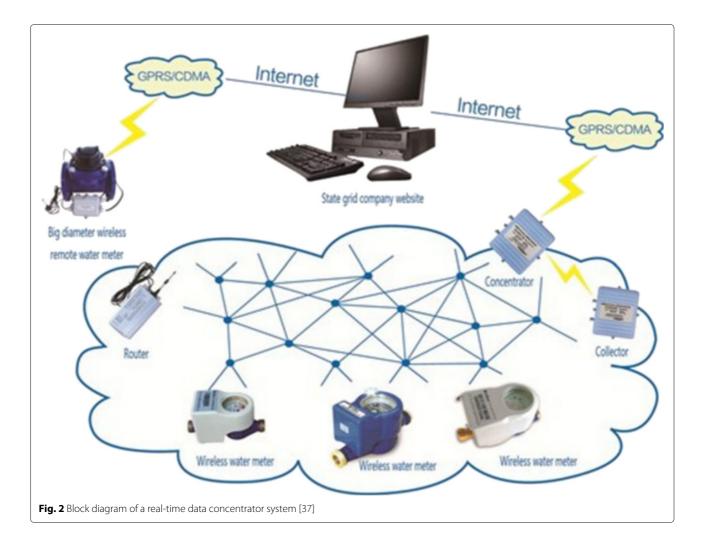

The flash memory is very much useful in fields where data transportation and archival is a key requirement. The memory can be used as a data concentrator (Fig. 2) where the proposed controller architecture along with the flash memory can be used as the removable memory of any data concentrator network device. The flash memory has extensive application in database [4], networking [5], biomedical application [6, 7], virtualized storage system [8], cloud computing [9], geographic remote sensing [10], mobile devices [11-13], etc. It can be used in a router to store the routing table for further access. NANDbased flash system is also widely employed as cache in virtualized system [8]. In such application scenarios, the efficiency of single and multiblock data transfer is very important which consequently affects the input-output operations per seconds (IOPS) measure of storage system. Generally, we wish to maximize this metric with respect to different types of flash as this indicates the measure of flash utilization. As stated, flash-based system can be used as a cache or a data concentrator or to cater any such storage requirements. However, here in the paper, we do not analyze the pros and cons of such utilization of flash in detail as the work mainly concentrates on efficient implementation of a controller for single or multiblock data transfer with respect to flash memory. The implementation may be exploited in any kind of flash resource utilization and will ultimately contribute in the calculation of the metric of memory resource utilization. Therefore, it is observed that the implementation of an efficient flashbased data transfer is a fundamental driving factor in the improvement of flash resource utilization and the paper is focusing on that rudimentary aspect.

The flash based cards like microSD, SD or SDHC cards work in two different bus modes. They are the Secure Digital (SD) bus mode and the Serial Peripheral Interface (SPI) bus mode. The SPI mode is a synchronous serial protocol with less complexity. It is extremely popular for interfacing the peripheral devices and no native-host interface is needed for this mode. For its simplicity and usefulness in the low cost embedded system application, we have considered designing an entirely on-board hardware-based controller for smooth realization of SPI bus mode-based data transfer protocol to communicate with the flash-based memory card

To date, we find that limited research work describes the design of data archival system and subsequent implementation using HDL [1]. In some research work, SPI mode-based data communication system has been implemented. Another work was proposed in the literature where the SDHC card had been used in SD mode (i.e., bulk data transfer mode) for video signal storage and processing [14]. With the newly emerging technologies, flash-based memory devices have been used as the efficient storage unit and till now it accomplishes the need of memory storage even on the modern era of technological advancement [2, 3, 15–23].

In light of the above, this paper proposes a novel, real-time, low-cost, system-on-chip application specific controller for multimedia data storage and retrieval to flash-based memory cards. The architecture of this real-time controller has been designed using FSM-based approach. The HDL used here is very high speed integrated circuit hardware description language (VHDL). Also, the design is such that there is no use of any on-chip general purpose processor (GPP), external controller, hardware resources, or any high-level languages during

the operation. The prototype has been entirely implemented in target FPGA board. The physical attribute of an FPGA chip, being compact in size and low in power consumption, makes it an ideal platform for the implementation. Also, we have tried to exploit the parallel processing capability of FPGA during design and implementation of various modules. Till date to the authors' knowledge, optimal-in-hardware implementation of such an application-specific controller and the study of its various modules were not explored in details by earlier research. In this work, the proposed controller has been examined for both the audio and video data storage and retrieval separately. Also to test the importance of the work with respect to practical workloads [24], we have collected the dataset from MSR Cambridge Traces [25], SNIA Iotta Repository [26], and UMass Trace Repository [27] and tried to establish the importance of the controller with respect to flash read-write

Again in nutshell, the objectives of this paper are as follows:

- To design a modular low-cost, system-on-chip, application-specific controller for multimedia data storage and retrieval to flash memory cards like SD, SDHC, and microSD card in SPI mode with less overhead.

- 2. The design is completely FSM based and the controller has been primarily realized using five different modules and a control unit. This five different modules, along with the control unit, are the different functional areas of the proposed system, which is implemented completely in a single chip.

- 3. When the card is in idle state, the system has an option of working in power saving mode.

- 4. The controller will work in real time, in modular fashion and the implementation is on a single FPGA. The proposed design tries to utilize the parallel processing capability of FPGA. No other external devices or on-card intelligent controller has been used for this implementation. Here, the prototype has been completely synthesized and tested for Spartan 3E xc3s500e-4-fg320 FPGA.

- 5. The architecture has been designed using HDL only. Here in this paper, we have considered VHDL for implementing the controller. No high-level languages were used for this design. This FSM-based design using VHDL is one of the basic feature of this proposed controller, which makes it faster than any other controller.

- 6. It is completely a prototype design of the proposed controller; the design can be implemented in any other platform instead of Spartan 3E target device (even using ASIC also) with a very minor modification in configuration part of the implementation. There will be no change in the design phase.

The rest of the paper is organized as follows. Section 2 introduces the related works and highlights the novelty of the proposed approach. Section 3 describes the proposed FPGA-based controller, its architecture, execution process, and overall operation of the controller. Section 4 presents the hardware-specific implementation and synthesis details for the target Xilinx Spartan-3E (xc3s500e-4-fg320) FPGA development platform. Experimental results are described in Section 5 and Section 6 concludes the paper.

### 2 Review of the related works

FPGAs have been used for prototype design in a range of engineering application [1, 14–19]; however, till date to the authors' knowledge, the design of a complete application-specific controller for different flash memory card access with detailed description of the modules and their operation is limited. Table 1 depicts some of the earlier work in this domain.

Elkeelany et al. [1] proposed an FPGA-based data archival system to SD card, using Verilog HDL and they accessed the card in SPI mode. Scalability issues have not been achieved in this design. They have partially applied FSM based approach and the implementation issues of different SD cards have not been discussed explicitly in this paper.

Yang et al. [14] presented the SDHC card video player based on SoPC technology. The IP core and two display buffer SRAMs were alternately utilized for their proposed design. They have accessed the SDHC card in SD mode for bulk data transfer. The proposed design has been implemented using high-level language.

In another work, Abdallah and Elkeelany [15] proposed a FPGA-based simultaneous multi-channel data acquisition system and they had verified the proposed architecture for analog signals. The design includes analog-to-digital converter to convert the analog signal to digital data. The time-critical tasks were implemented in hardware, while the other tasks were implemented using

**Table 1** Existing papers on SD card controller design

| Work       | Controller design                                                   | Platform model                                                   |

|------------|---------------------------------------------------------------------|------------------------------------------------------------------|

| [1]        | Data archival to SD card using HDL                                  | Altera Cyclone II                                                |

| [14]       | Design of SDHC card video player on SoPC                            | NIOS II CPU with IDCT<br>hardware acceleration IP<br>core        |

| [15]       | Simultaneous<br>multi-channel data<br>acquisition system            | Altera Cyclone II                                                |

| [16]       | NAND flash memory<br>controller for SD/MMC<br>card                  | Freescale DSP 56858<br>platform with UMC 0.18<br>µm CMOS process |

| [17]       | Portable analog data<br>capture using custom<br>processing          | WOLFSON WM8731 ADC,<br>NIOS-II processor                         |

| [18]       | A high efficient flash<br>storage system for<br>two-way cable modem | TWCNP-OS                                                         |

| [Proposed] | FSM-based<br>application-specific<br>controller using HDL           | Xilinx Spartan 3E<br>xc3s500e-4-fg320                            |

embedded C. The use of the high-level language in this paper makes the system slower with additional overhead.

Lin and Dung [16] proposed a novel NAND flash memory controller for SD/Multimedia Card (MMC). They have designed Bose-Chaudhuri-Hocquenghan (BCH) error correction code (ECC) [28] for correcting the random bit errors of the flash memory chip. The UMC 0.18  $\mu m$  CMOS process was used to implement the proposed memory controller chip. This proposed controller was verified for MMC only.

Elkeelany and Vince [17] proposed a portable analog data capture system using custom processor. The SD card had been used in 1-bit SD mode for their proposed system. The SPI mode or 4-bit SD mode-based communication were not discussed in their design.

The works, summarized in Table 1, have established the concept of FPGA-based implementation for the SD card data archival system either in SD mode or SPI mode. Some researchers [15–18] have taken help of highlevel languages or external controllers, on-board processors, and other resources apart from only FPGA logic resources during implementation of data access mechanism. In some paper [14, 15, 23, 29, 30], partially, FSM-based approaches have been used for realization of data transfer mechanism. The single/multiple blocks read/write procedures were designed using FSM, and they have been implemented those procedures using HDL for target device. Also, the BCH code for NAND flash memory has been optimized in previous work [31] and the data-intensive application using FPGA has been performed in earlier researches [32, 33].

Flash-based storage system has other advantages also. Many a time, it has been observed that the efficient data communication of flash-based system plays a significant role in the improvement of flash resource utilization in many of the systems. Flash resource can be utilized as a cache-based storage system or can be integrated with hard disk drive (HDD) and can act as a hybrid system. Flash resources are also utilized in virtualized storage system [8] where efficient managers are designed to get more high cost effectiveness than normal caching algorithm. Flashbased multi-tiered systems are also studied presently in the literature. Some of them are multi-tier SSD-based solution [34], a hyper-visor-based design [35] etc. Most of the works, however, emphasize on the improvement of caching policies with respect to standard existing caching algorithm like LRU and that analysis is out of scope of this paper. Here we primarily analyzed on multimedia data storage and retrieval to flash-based storage system and this in turn has profound effect on the improvement of flash-based resource implementation.

In our work, we aim to design an applicationspecific controller for efficient multimedia data communication with flash-based cards in SPI mode and the controller architecture was entirely designed using FSMbased approach. There are mainly five states present in the proposed FSM and the states are named as initialization state, idle state, card-read state, card-write state, and decision-making state. During the realization of the controller architecture, these states are mapped into the modules of the controller. Now some of these modules are used to accomplish card read/write procedures and therefore internal architecture of those modules are again implemented based on FSM format for the realization of above procedures. Note that the proposed architecture and implementation aims to minimize both the clock utilization and on-board resource utilization of the FPGA board. Also in this work, we have considered the required clock cycles, workload, response time, etc. as performance metric to compare the effectiveness of the proposed approach with respect to other existing papers. However, only in the initialization phase, we have represented the performance with respect to "time" metric to compare the achieved results with the reported values in the literature.

### 3 Proposed FPGA-based controller

This section initially describes the basic characteristics of the SD/SDHC card and microSD card and then introduces the proposed controller in rest of the section.

### 3.1 High capacity SD card

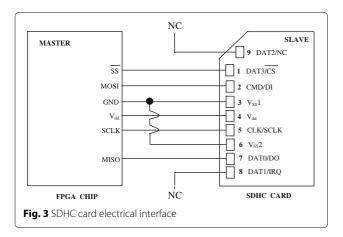

The SD/SDHC card communication is based on the advanced nine pin interface, i.e., Clock, Command line/Master Out Slave In (MOSI), 4xData lines/ Master In Slave Out (MISO), and 3xPower lines. The card supports three communication protocols [21]. They are SD 1-bit mode, SD 4-bit mode, and SPI (Serial Peripheral

Interface) mode. Table 2 shows the pin configuration of the SD/SDHC card and Fig. 3 shows the thematic representation of electrical interface of the card (slave) in SPI mode with the FPGA board (Master).

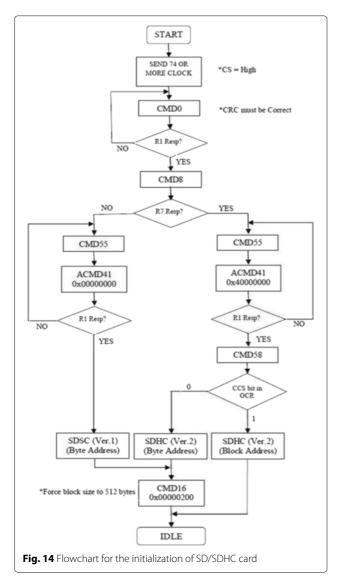

The SD/SDHC card communication protocol in SPI mode is entirely a command-dependent protocol and the card responds to every command with a pre-defined response pattern. In the way of initialization, first the card is initiated with CMD0 command. Then, the controller validates the voltage range by generating the CMD8 command. It also identifies the version of the card (version 2 (SDHC) card or some other cards). Subsequently, the controller generates the application-specific commands such as (CMD55 + ACMD41) to complete the initialization process. The controller will continuously generate (CMD55 + ACMD41) command until the card initializes itself by giving a "00000000" response. The SDHC card supports two types of addressing mode. They are block addressing mode and byte addressing mode. The CMD58 command identifies the addressing mode of the version 2 SDHC card. Also, CMD16 command is issued to fix the data block length to 512 bytes. After initialization process, the card goes to the idle state until the next command is being generated for single/multiblock read/write.

The speed class of the card denotes minimum writing performance of the card to record a video normally [36]. Various speed classes defined by SD Association are 2, 4, 6, and 10. Throughout this work, we have used the SDHC and SD card with speed classes 4 and 2, respectively, which means that the SDHC and SD card, used in this purpose, supports minimum 4 and 2 MB/s writing speed, respectively, for video recording.

### 3.2 MicroSD card

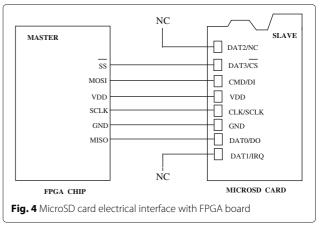

The microSD card communication is much similar to the SD card communication. The difference between these two monsters in the present age data storage medium is in their pin configuration. The microSD communication is based on the 8-pin interface where all the pins from the SD card are present except the second ground (Vss2) pin.

Table 2 SD/SDHC card pin details

| Pin No. | Name      | Function in SD mode | Function in SPI mode          |

|---------|-----------|---------------------|-------------------------------|

| 1       | DAT3/(CS) | Data line 3         | Chip select/slave select (SS) |

| 2       | CMD/DI    | Command line        | MOSI                          |

| 3       | Vss1      | Ground              | Ground                        |

| 4       | VDD       | Supply voltage      | Supply voltage                |

| 5       | Clock     | Clock               | Clock (SCLK)                  |

| 6       | Vss2      | Ground              | Ground                        |

| 7       | DAT0/DO   | Data line 0         | MISO                          |

| 8       | DAT1/IRQ  | Data line 1         | Unused/IRQ                    |

| 9       | Dat2/NC   | Data line 2         | Unused                        |

Table 3 shows the pin details of the microSD card, and Fig. 4 shows the interfacing of the microSD card with the Spartan3E target FPGA board.

The microSD card communication is also based on command-dependent protocol, and it is almost similar to the SD and SDHC card communication methods. The capacity of the microSD card denotes how it works. If the capacity is less than or equal to 2 GB ( $\leq$  2 GB), then the card works similar to the SD card; otherwise, the principle of operation is the same as the SDHC card.

The definition of the speed class for microSD card is the same as the SD card [36]. We have used the class 4 microSD card throughout the work, which means, the card supports 4 MB/s writing speed for video recording in a normal mode.

### 3.3 Architecture of the proposed controller

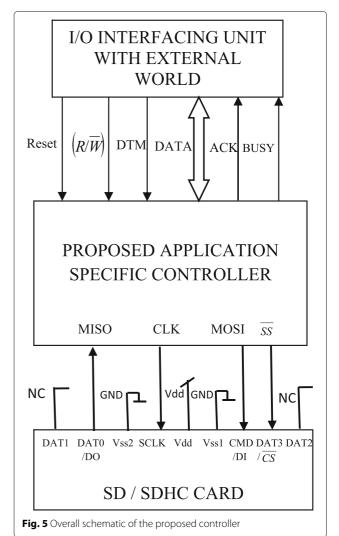

The workflow of the proposed host controller is based on the initialization of the card followed by data transfer (read/write) sequences. The overall external view of the controller interfacing the SDHC/SD card is given in Fig. 5. The same process can be used for interfacing the microSD card also. The Vss2 pin remains unconnected when the process is used for interfacing the microSD card as the card contains only 8-pin interface, and the Vss2 pin is not present in the physical architecture of the microSD card.

Table 3 MicroSD card pin details

|         |           | 1                   |                                              |

|---------|-----------|---------------------|----------------------------------------------|

| Pin No. | Name      | Function in SD mode | Function in SPI mode                         |

| 1       | Dat2/NC   | Data line 2         | Unused                                       |

| 2       | DAT3/(CS) | Data line 3         | Chip select/slave select ( $\overline{SS}$ ) |

| 3       | CMD/DI    | Command line        | MOSI                                         |

| 4       | VDD       | Supply voltage      | Supply voltage                               |

| 5       | Clock     | Clock               | Clock (SCLK)                                 |

| 6       | GND       | Ground              | Ground                                       |

| 7       | DAT0/DO   | Data line 0         | MISO                                         |

| 8       | DAT1/IRQ  | Data line 1         | Unused/IRQ                                   |

|         |           |                     |                                              |

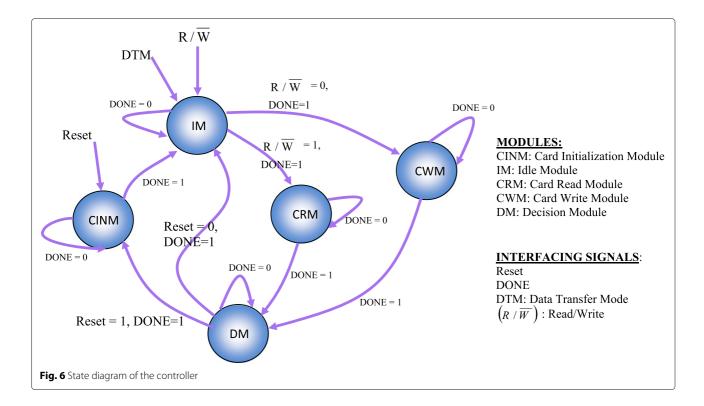

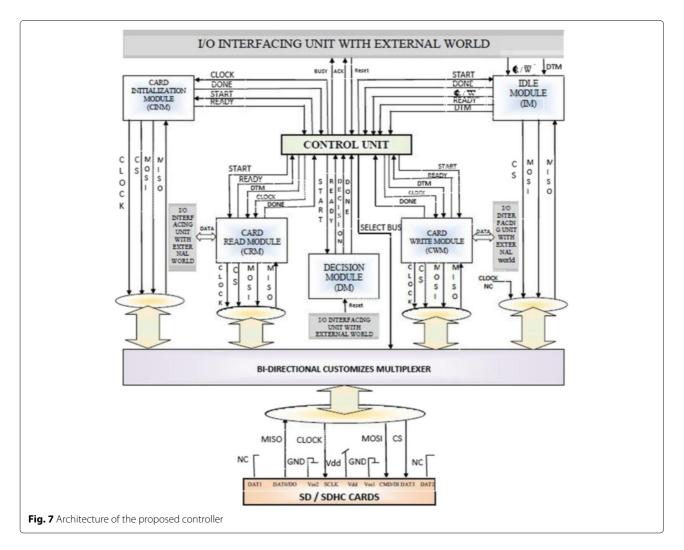

The state diagram of the overall control flow of the controller is shown in Fig. 6, and the internal architecture is shown in Fig. 7. The state diagram of Fig. 6 is working as a backbone for the architecture of the controller. The complete architecture has been implemented using VHDL.

As we observe from the above mentioned flow sequence and the schematic of the internal architecture, the proposed controller is divided into five different modules. They are card initialization module (CINM), idle module (IM), card read module (CRM), card write module (CWM), and decision module (DM). Along with the above modules, a control unit (CU) is there to monitor and control the activities of each module and the flow of respective driving signals. The CU operates based on the FSM shown in Fig. 6.

Each of the modules and CU contains several internal and external data and control lines. The communication with the external world is done by the controller either using I/O interfacing units or a customized multiplexer. The Reset, DTM (Data Transfer Mode),  $R/\bar{W}$ , DATA, ACK, and BUSY signals are interfaced with the controller via I/O interfacing unit. The Reset signal, connected with CU, initiates the data storage or retrieval operation. DTM signal selects the single/multiblock data transfer mode of the controller, R/W is used for read/write operation selection, and a 8-bit bidirectional DATA bus is used for communication with external world. Also, other signals like Clock, Chip Select (CS), MISO, and MOSI signals are connected between SDHC card and the controller through a  $(4\times1)$  bi-directional customized multiplexer where each input line of the multiplexer is a 4 bit width data bus. Each data bus consists of Clock, Chip Select ( $\bar{CS}$ ), MISO, and MOSI signals. These four input buses of the multiplexer connect the four modules, say, CINM, IM, CRM,

and CWM of the controller with the external card based on the SELECT bus. The output bus from the multiplexer communicates with the card. Only in the data bus from the IM, the clock signal remains unconnected to realize the power saving mode of the controller. Therefore as a whole, the designed multiplexer has 2 bit SELECT bus (S1 and S0), 4 input bus lines ( $4 \times 4 = 16$  lines) and one output bus line ( $1 \times 4 = 4$  lines). SELECT bus connected with the multiplexer in sequence helps to communicate the individual modules with the card, and CU controls the entire selection process. The module selection activities of the SELECT bus is described in Table 4.

BUSY and ACK are the two status signals present in the controller and they are connected with CU. The BUSY signal represents the busy state of the controller and ACK signal acknowledges any assigned work accomplished by the controller. On completion, the module deactivates the BUSY signal and activates the ACK signal to intimate the user that the task has been completed successfully. Failure to complete any assigned task makes both the BUSY and ACK signal de-asserted. The activity of the signals is tabulated in Table 5.

The CU also internally communicates with every module in sequence for efficient data transfer with the card. The common signals for all the modules are Reset, CS, and clock signal. The CS and clock signals are also supplied to the card via multiplexer. Once Reset signal is received by CU, it issues a START signal to the CINM along with the clock signal. CU also issues START and clock signal

for the other modules when they are about to initiate their action. In idle state, no clock is received by the modules and thus they work in power saving mode. Once a module receives a START signal, it acknowledges so by issuing a READY signal to the CU and starts working. After every successful completion of the work, the module intimates CU with DONE signal.

CU starts working with the card initialization module. On receiving the Reset signal, CU activates the CINM and it issues the initialization commands to the card in order to initialize it in SPI mode. The card responds to every command and on completion of initialization procedure, the module receives the final response from the card.

**Table 4** Table for SELECT bus activity

|    | •  |                 |

|----|----|-----------------|

| S1 | SO | Selected module |

| 0  | 0  | CINM            |

| 0  | 1  | IM              |

| 1  | 0  | CRM             |

| 1  | 1  | CWM             |

After successful initialization of the card, the control transfers to IM with the START signal. The IM continuously monitors the  $R/\bar{W}$  and DTM signal.  $R/\bar{W}$  signal specifies whether the next operation will be card read or card write. The DTM signal will intimate the IM regarding the single/multiblock data transfer. Whenever it receives the  $R/\bar{W}$  signal, it passes both the  $R/\bar{W}$  and DTM value to CU and goes to the idle state by sending a DONE signal. Depending on the  $R/\bar{W}$  signal, the CU transfers the control either to CRM or to CWM.

The CU generates different command sequences for either of these modules. In card read sequence, the CRM reads the data block from the card along with the CRC bits and publish it to the I/O interfacing unit. In card write

**Table 5** Table for the status signal activity

| BUSY | ACK | Controller status                         |

|------|-----|-------------------------------------------|

| 0    | 0   | Time out, controller failed to read/write |

| 0    | 1   | Task successfully accomplished            |

| 1    | Χ   | Controller is busy                        |

sequence, the CWM receives the data block as an input from the I/O interfacing unit and writes the received block along with CRC to the card and receives the CRC response from the card. After read/write operation, CRM/CWM issues a DONE signal and itself goes to the power saving mode. Finally after completion of entire data transfer, controller generates the ACK signal to the external world through the I/O interfacing unit to intimate that the work is successfully completed.

The DM monitors the Reset signal received from the I/O interfacing unit during operation. Assertion of Reset signal means that CU will again reinitialize the process by activating the CINM. If the Reset signal remains deasserted, then the CU will activate the IM and again follow the previous sequence of operation for continuous data transfer. The DM gives its decision to the CU by the DECI-SION signal and goes to power saving mode by issuing a DONE signal.

### 3.4 Overall system operation

The flow of execution and communication between the individual units of the controller and SDHC card is now described. The similar procedure is also applicable for SD and microSD card-based data storage and retrieval. All of them actually works in three different phases namely card initialization phase, card read phase, and card write phase. Previously stated five modules are the astringent of these three phases. The controller communicates with the external world through the I/O interfacing unit and the customized multiplexer. The controller initiates its operation on reception of Reset, DTM, and R/W signals and sends the signals to CU. Then it intimates regarding its status using the BUSY and ACK signal. When the controller is busy in processing some task, it makes the BUSY signal high until the task is accomplished. After every successful completion of a process, the controller informs the outer world by asserting the ACK signal and de-asserting the BUSY signal. If the controller fails to complete the task given, then it de-assert both the BUSY and ACK signal. Table 5 describes the operation of the two status signals.

The pseudo-code for the data transmission process to the card is given in Figs. 8, 9, 10, 11, 12 and 13, and the FSM of the controller and the architecture are essentially inspired form the activities described in the codes. The rest of the section describes the operation of different modules.

Card initialization module (CINM): The CINM initiates the SDHC card in SPI mode. Figure 14 contains the FSM of the initialization module. The START signal activates the CINM and it acknowledges the CU with READY signal. The module first elapses 74 or more clock cycles for initiating the card in SPI mode. Then, the commands are generated to complete the initialization process. After completion of the initialization process, the controller

### Power on initialization of the system

- 1. Power on

- 2. If reset = '1' then

- 3. Start Initialization (internal signals and states)

- 4. Else

- Start Initialization (Card)

- 6. End if;

Fig. 8 Psudo-code for power on sequence

validates the addressing type for the SDHC card (either block addressing or byte addressing) by asking to publish its card capacity status (CCS) bit in operational control register (OCR). The high value of the CCS bit in OCR register means that the card is a version 2 SDHC card supporting block addressing mode, and the low value of CCS bit refers the version 2 (SDHC) card supporting byte addressing mode. If the result matches with byte addressing mode, the controller then generates the next command to forcefully make the block length to 512 bytes. On completion of the initialization process CINM will issue a DONE signal.

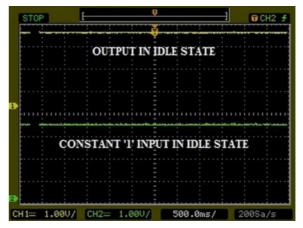

Idle module (IM): The idle module works in two modes. They are polling mode and control transfer mode. IM continuously polls the  $R/\bar{W}$  signal and DTM signal. Depending upon the status of these two controlling signals, CU transfers the control either to CRM or to CWM. On completion of the operation, the DONE signal is asserted to CU. On polling mode, the controller is in power saving state as the card is in the idle state. The controller sends a constant high value to the MOSI line, and the card also responds with a constant high value via MISO line of the controller.

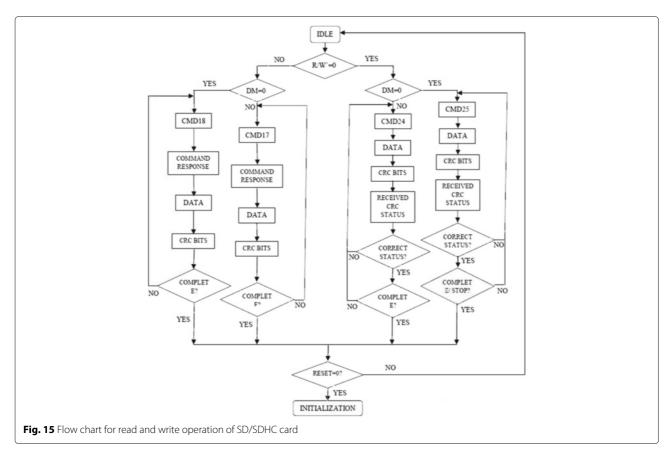

Card read module (CRM): The SDHC and similar type of cards support two types of data transfer, one is the single block data transfer and another is the multiblock data transfer. The left branch of the flow chart in Fig. 15 describes the read operation from the card. The CRM has been designed to read the data blocks from the SDHC card. The CU issues two different commands for CRM

### Initialization (card) in SPI mode

- 1. Send initialization commands

- 2. If received final response = TRUE then

- Go to IDLE state

- 4. Else

- Resend Initialization commands

- 6. End if:

Fig. 9 Psudo-code for initialization (card)

### Idle state

- If wr = '1' then

- Go to Card Write process

- Elsif rd = '1' then

- Go to Card Read process

- 5. Else

- Remain in IDLE state

- 7. End if;

Fig. 10 Psudo-code for idle state

depending upon the DTM signal value. One is for single block data transfer and another is for multiblock data transfer. MOSI line of the controller is connected with the CMD/DI line of the card, and similarly MISO line of the controller is connected with DAT0/DO line of the card. After successful transmission of the command via MOSI line of the controller, CRM receives the command response from the card through MISO and then starts reading the data block(s) from the card along with the CRC bits. The block transfer is preceded by a start block token "11111110" along with a block of data, which is followed by the CRC.

The multiple block transfer can be terminated by the command CMD12, generated by the controller.

*Card write module (CWM)*: The CWM has been designed to write the data block to the SDHC card. The right branch of the flow chart in Fig. 15 describes the write

### **Card Write Process**

- 1. If data mode = '1' then

- 2. Send single block write command

- Else

- 4. Send multi block write command

- End if;

- 6. If received response = TRUE then

- 7. Go to decision process

- 8. Else

- Restart Card Write process

- 10. End if;

- Fig. 11 Psudo-code for card write process

### Card Read Process

- 1. If data mode = '1' then

- 2. Send single block read command

- 3. Else

- Send multi block read command

- 5. End if;

- 6. If read process completed then

- 7. Go to decision process

- 8. Else

- Restart Card Read process

- 10. End if;

Fig. 12 Psudo-code for card read process

operation. On the way of execution, CU transfers the control to CWM along with the DTM signal to ensure a single block data write or a multiblock data write. In this implementation, both single and multiblock write operation have been taken into consideration. For single block write operation, the controller generates the command with the starting address and then it starts writing 512 bytes of data. For multiblock write, the controller writes the data block until the CMD12 stop command is being issued. The CRC bits are appended to each data byte for the entire write operation. The card sends back the response pattern in the MISO line of the controller, where "XXX00101" means the data block is accepted, "XXX01011" means the data block is rejected due to the CRC error, and "XXX01111" indicates that the data block is rejected due to the flash program error (in the pattern, "XXX" means do not care bits). The multiple block write improves the

### **Decision process**

- If reset = '1' then

- Start Initialization (card)

- Else

- 4. Go to IDLE state

- 5. End if:

- Fig. 13 Psudo-code for decision process

throughput as a single command is generated for bulk of data blocks write procedure.

Decision module(DM): The DM has been designed to decide the destination of the controller after completing the data transfer operation viz. whether the control will go to the IM or to the CINM. It is required for successive sequence of data transfer. After performing the data transfer process, the control comes to the DM. The DM constantly monitors the Reset signal and depending on the status of the Reset signal, it decides whether the control will go to the IM for performing the next data transfer operation or it will go to the CINM for initialization of the card.

The ACK signal is finally issued by the controller through the I/O interfacing unit, to intimate the user that the work given to the controller has been completed successfully and it is ready to process next set of operation.

### 4 Hardware-specific implementation details

To explore the feasibility of the proposed architecture, the FPGA-based controller was implemented with the help of synthesizable VHDL. This actually reduces the processing time of the proposed controller than any other high-level languages. The target development platform is based on Spartan-3E (xc3s500e-4-fg320) FPGA chip. The card has been accessed through a multi-port card reader connected with the target FPGA board using 6-pin cable. A SanDisk 8 GB SDHC card, a Cannon 16 MB SD card, and a 2 GB microSD card, with speed classes 4, 2, and 4, respectively, have been used for testing and verification of the proposed controller.

### 4.1 Application-specific controller initialization challenges

From the hardware point of view, traditionally, the personal computer accesses the flash memory through a permanent device interface, which implies a fixed point access of the memory. In this proposed design, the system comes up with a detachable unit to be connected with the memory card so that the card can be accessed anywhere.

Now from the designers' point of view, synchronization of clock throughout the design is a big challenge to the designer as the flash memory card requires 100- to 400-KHz clock frequency for the application specific command execution during initialization [3] and maximum 25-MHz clock frequency for data transfer [1]; which ultimately points to the decrement of clock frequency and it implies sacrifice in performance in a single clock input system. If the clock frequency does not match in initialization process, then the card uses to poll the command in a 50-ms time gap to complete the initialization process.

### 4.2 Synthesis details

The design was successfully synthesized using Xilinx ISE version 14.1 for the Spartan-3E XC3S500C target device, and then it was compiled and built for implementation. This process consists of translating, mapping, placement, and routing of the signals. For the design implementation process, no partition was specified and the design was translated and mapped successfully. All signals were placed and routed successfully as well; all the timing constraints were met. Five percent of the total logic slices on the device was utilized for this implementation. Brief description of the resource utilization during implementation is given in Table 6.

The number of logic slices utilized for the proposed controller is 226 out of 4656 (5%).

### 5 Experiments and results

In this section, we have tested the working performance and efficiency of the proposed controller extensively for different synthetic dataset and practical work loads. Initially, we have defined the metrics used to evaluate

the performance of the controller. Subsequently, different synthetic and practical workloads were described as case studies of the paper.

### 5.1 Performance metrics

In this paper, we have used following metrices to evaluate the performance of the controller. They are defined as follows.

Clock cycle taken per process (CCTPP): In order to make the performance evaluation of the proposed controller independent of system clock and other system specific parameters, we have described the performance of the controller in terms of clock cycles. Here, CCTPP describes the clock cycle taken by an individual process to successfully complete a process. If we navigate the proposed design into multiple systems, then CCTPP parameter will be system independent.

**Table 6** Resource utilization during implementation

| g                     |                       |                            |                 |  |

|-----------------------|-----------------------|----------------------------|-----------------|--|

| Logic blocks          | Number of logics used | Number of logics available | Utilization (%) |  |

| Logic slices          | 226                   | 4656                       | 5               |  |

| Slice flip/flops      | 167                   | 9312                       | 2               |  |

| Slice LUTs            | 421                   | 9312                       | 6               |  |

| Clock buffer          | 1                     | 24                         | 4               |  |

| Number of bonded IOBs | 15                    | 232                        | 6               |  |

Time taken per process (TTPP): This is the time taken by the individual process to accomplish the task assigned successfully. We have used the conventional units of time to define the TTPP.

Input/output operations per seconds (IOPS): IOPS is a measurement process used to characterize the storage devices like flash storage memory. The IOPS is not defined independently and it is a combination of three metrics. Along with IOPS other two metrics, say response time and workload metrics are also defined to characterize the performance of the memory module.

### 5.2 Simulation details

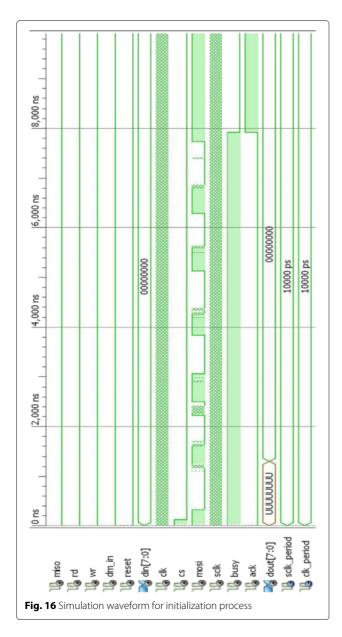

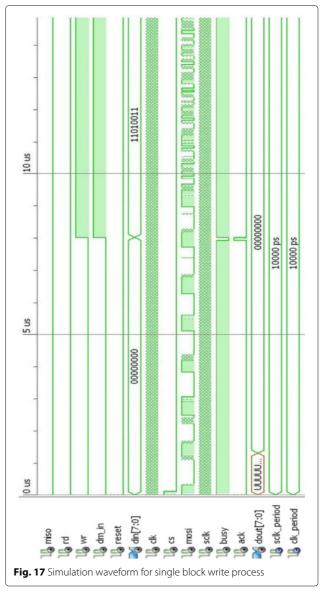

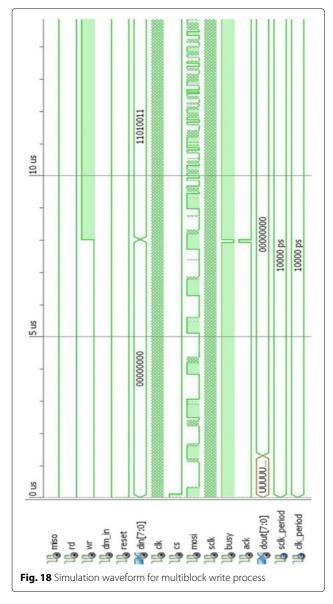

The proposed architecture was first simulated in the Xilinx ISE 14.1 virtual environment for initial verification. In this phase, Fig. 16 gives the waveform representation of the initialization process completely. Figure 17 represents the timing diagram representation of the single block write, and Fig. 18 gives the timing diagram representation of the multiblock data write operation. The simulation results are only feasible for data write operation and the implementation section represents the entire results for initialization and both the read/write operation. Table 7 elaborates the different abbreviation of the input and output ports used to simulate the design.

### 5.3 Implementation details

The proposed controller has been tested using various case studies with different type of input data pattern.

### 5.3.1 Case studies

Seven different case studies have been performed to verify the effectiveness of the proposed controller for SD, SDHC, and microSD cards with varying volume size of the data. For first four cases, synthetically, text, audio, and video patterns were generated. Other three datasets were taken from practical workloads representing block I/O traces from MSR Cambridge Traces [25], SNIA Iotta Repository [26], and UMass Trace Repository [27].

Case I: pre-declared embedded data pattern: The first case study uses a pre-declared embedded data pattern

with 8-bit data. The proposed controller tests the basic read/write operation for a Cannon 16 MB SD card using this data pattern. The same 8-bit data pattern has been written repeatedly to the SD card for testing the single and multiblock data write operation. Later on, the same data pattern has been retrieved to validate the single as well as multiblock data read operation from the same SD card.

Case II: pseudo-random number sequences: The second case study has been performed for testing the proposed controller for SDHC card. A pseudo-random number (PRN) generator has been designed to generate 8-bit random data pattern continuously to perform the single block as well as the multiblock write operation for a SanDisk 8 GB SDHC card. The previously used Cannon 16 MB SD card and a 2 GB microSD card have also been tested for single and multiblock read/write operation using those PRN sequences.

Case III: audio signal transmission: The third case study has been performed for testing the efficiency of the proposed controller with continuous data transfer. An analog signal in audio range is fed to an on-board LTC 1407A analog-to-digital converter (ADC) [20]. The digital data at the output of the converter is fed to the controller for data storage and retrieval. The LTC6912-1 available in the on-board ADC provides two independent inverting amplifiers with programmable gain to maximize the conversion range of the ADC to  $1.65 \pm 1.25$  V. The gains for both the channels are independently programmable using a 3-wire SPI interface to select voltage gains among "0," "-1," "-2," "-5," "-10," "-20," "-50," and "-100" V/V (LTC6912-1) [20]. The analog-to-digital conversion formula is given below in Eq. 1:

$D[13:0] = GAIN \times [(V_{IN} - 1.65 \text{ V})/1.25 \text{ V}] \times 8192 \text{ (1)}$

**Table 7** Abbreviation of the ports in simulation waveform

| Abbreviation Full name |                     |

|------------------------|---------------------|

| miso                   | Master in slave out |

| rd                     | Read                |

| wr                     | Write               |

| dm_in                  | Data mode selection |

| reset                  | Reset               |

| din                    | Data in             |

| clk                    | Clock               |

| CS                     | Chip select         |

| mosi                   | Master out slave in |

| sclk                   | Slave clock         |

| busy                   | Busy signal         |

| ack                    | Acknowledgment      |

| dout                   | Data out            |

Here, D[13:0] represents the 14-bit 2's complement value of the analog input. The maximum sample rate for the ADC is approximately 1.5 MHz [20]. The 14-bit digital output from the ADC has been compressed to 8-bit digital data pattern, so that the proposed 8-bit controller can easily read the data byte for storing into the SDHC memory card. On later phase, the retrieval of the stored data from the same SDHC card indicates the memory read operation for the analog signal.

Case IV: video signal transmission: The fourth case study is performed with video signal storage and retrieval. The on-board DB15 VGA connector port [20] has been used to display the video frames in a CRT monitor. The VGA signal timing is specified, published, copyrighted, and sold by the Video Electronics Standards Association (VESA) [20]. Thus in this paper, the detail specifications of the processing video signals are not mentioned in depth.

The frames of the video signal have been generated and then decoded in the binary-numbered matrix. Then, the data from the generated matrix have been stored in the card for testing the card write operation. Here, the multiblock data write operation has been performed as the volume of data is too high to perform the single block write operation. On later phase, the previously written data have been retrieved from the same card for validating the multiblock card read operation process. The FPGA board was connected with a CRT monitor through a VGA cable for displaying the retrieved result (i.e., the video signal) from the card. The CRT monitor, used in this case study, has the horizontal frequency of 90 kHz and the screen resolution of  $1024 \times 768$  pixels with color quality of 16 bits. So, the refresh rate of the monitor is 72.

Case V: dataset from MSR Cambridge Traces: The Microsoft Research (MSR) Cambridge traces [25] are a commonly used data repository, built by Microsoft research group. This repository was formed to advance

the state of the art computing and also to solve the practical world problems through technological innovation. This is a collaboration of the academics with the government and industry researchers. There are 35 different traces available for this MSR Cambridge Traces and they represent 1-week block I/O traces of enterprise servers at Microsoft Research Cambridge. The characteristics of the traces are given along with file names, their attributes, file size, etc. in Table 8. We have used those datasets to check the performance of the proposed controller in multiblock

**Table 8** Characteristics table for MSR Cambridge Repository [25]

| Repository name | Abbre-<br>-viation | File name         | File size<br>in KB | Attributes |

|-----------------|--------------------|-------------------|--------------------|------------|

| MSR             | M11                | CAM-02-SRV-lvm0   | 227,577            | Timestamp  |

| Cambridge       | M12                | CAM-02-SRV-lvm1   | 1,576,883          | Hostname,  |

| 1               | M13                | CAM-02-SRV-lvm2   | 117,104            | Disk       |

|                 | M14                | CAM-02-SRV-lvm3   | 1,274,935          | Number,    |

|                 | M15                | CAM-02-SRV-lvm4   | 1,274,935          | Туре,      |

|                 | M16                | CAMRESHMSA01-lvm0 | 197,530            | Offset,    |

|                 | M17                | CAMRESHMSA01-lvm1 | 29,069             | Size,      |

|                 | M18                | CAMRESISAA02-lvm0 | 643,399            | Response   |

|                 | M19                | CAMRESISAA02-lvm1 | 8,832,021          | Time       |

|                 | M110               | CAMRESWMSA03-lvm0 | 62,457             |            |

|                 | M111               | CAMRESWMSA03-lvm1 | 86,267             |            |

|                 | M112               | CAM-USP-01-lvm0   | 284,762            |            |

| MSR             | M21                | CAM-01-SRV-lvm0   | 115,703            | Timestamp  |

| Cambridge       | M22                | CAM-01-SRV-lvm1   | 2,393,907          | Hostname,  |

| 2               | M23                | CAM-01-SRV-lvm2   | 560,593            | Disk       |

|                 | M24                | CAMRESIRA01-lvm0  | 75,897             | Number,    |

|                 | M25                | CAMRESIRA01-lvm1  | 739                | Type,      |

|                 | M26                | CAMRESIRA01-lvm2  | 10,894             | Offset,    |

|                 | M27                | CAMRESSDPA01-lvm0 | 2,028,692          | Size,      |

|                 | M28                | CAMRESSDPA01-lvm1 | 2,476,675          | Response   |

|                 | M29                | CAMRESSDPA01-lvm2 | 98,864             | Time       |

|                 | M210               | CAMRESSDPA03-lvm0 | 80,578             |            |

|                 | M211               | CAMRESSDPA03-lvm1 | 34,773             |            |

|                 | M212               | CAMRESSDPA03-lvm2 | 61,550             |            |

|                 | M213               | CAMRESSTGA01-lvm0 | 103,206            |            |

|                 | M214               | CAMRESSTGA01-lvm1 | 113,632            |            |

|                 | M215               | CAMRESTSA01-lvm0  | 91,123             |            |

|                 | M216               | CAMRESWEBA03-lvm0 | 105,051            |            |

|                 | M217               | CAMRESWEBA03-lvm1 | 8,308              |            |

|                 | M218               | CAMRESWEBA03-lvm2 | 299,650            |            |

|                 | M219               | CAMRESWEBA03-lvm3 | 1611               |            |

|                 | M220               | CAMWEBDEV-lvm0    | 58,850             |            |

|                 | M221               | CAMWEBDEV-lvm1    | 55                 |            |

|                 | M222               | CAMWEBDEV-lvm2    | 9369               |            |

|                 | M223               | CAMWEBDEV-lvm3    | 35                 |            |

data transfer procedure. The SanDisk 8 GB SDHC card has been used as the flash storage in this case study.

Case VI: dataset from UMass Trace Repository: The UMass Trace Repository [27] is a commonly used data repository. It provides storage, network, and other traces for analysis to the research community. This work is supported by the National Science Foundation. This repository contains different traces namely CPU and memory, network, Storage, weather, power, smart, and multimedia traces under two different categories, namely Financial and WebSearch. The characteristics of the traces are given in Table 9. We have used those datasets to verify the multiblock data transfer process of the proposed controller and the SanDisk 8 GB SDHC card has been used for this purpose.

Case VII: dataset from SNIA lotta Repository Historical Section: Storage Networking Industry Association (SNIA) Iotta Repository [26] is a commonly used repository, used to store, manage, and distribute different traces or datasets for storage. The historical section of this repository includes all the traces which are older than 10 years. The historical section contains five different traces namely Block I/O Traces, Network File System Traces, Parallel Traces, Static Snapshots, and System Call Traces. Each of these traces are further divided into multiple sub-traces. We have used some sub-traces from those available traces to verify the multiblock data transfer process of the proposed controller. The characteristics of the traces are given in Table 10. The SanDisk 8 GB SDHC card has been used as the storage device in this case study.

Different flash transition layer settings: The functionality and efficiency of the proposed controller have also been tested using different volume of data. We have tested the read-write operations of the controller for different volume likely 4, 8, 10, and 512 MB and 1 GB.

### 5.3.2 Results

The implemented architecture of the proposed controller works in three different modes; namely card initialization mode, card read mode, and card write mode. After card initialization, based on the external commands, controller communicates with the card either for read or for write operation.

**Table 9** Characteristics table for UMass Repository [27]

| Repository name | File name  | File size<br>in KB | Attributes     |

|-----------------|------------|--------------------|----------------|

| UMass           | Financial1 | 151165             | ASU,           |

|                 | Financial2 | 102873             | LBA,           |

|                 | WebSearch1 | 30744              | Size,          |

|                 | WebSearch2 | 135948             | Opcode,        |

|                 | WebSearch3 | 127520             | Timestamps,    |

|                 |            |                    | Optical fields |

**Table 10** Characteristics table for SNIA Historical Section Repository [26]

| Trace name         | Sub-traces                   | Number<br>of files |

|--------------------|------------------------------|--------------------|

| Block I/O Traces   | Cello 1999                   | 12                 |

|                    | Cello 1996                   | 12                 |

|                    | Cello 1992                   | 12                 |

|                    | HP LAJW                      | 12                 |

|                    | Cello 1991                   | 12                 |

| NFS Traces         | Animation dataset            | 140                |

|                    | Harvard SOS Traces           | 7                  |

| Parallel Traces    | Sprite Traces                | 1                  |

| Static Snapshots   | Multimedia file sizes        | 1                  |

|                    | Microsoft Longitudinal Study | 1                  |

|                    | Microsoft 1998 Static Study  | 1                  |

| System Call Traces | LASR Traces                  | 13                 |

|                    | Seer Traces (ASCII)          | 1                  |

|                    | Seer Traces                  | 1                  |

|                    | CMU DFS Traces               | 14                 |

To validate the read/write operation two types of test unit has been considered. They are described as follows:

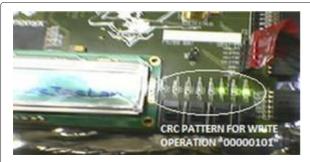

*Test unit: on-board output unit (LED)*: The Spartan 3E target FPGA board contains 8-bit output unit with 8 onboard light emitting diodes (LEDs) [20]. In the testing setup of the experiment, the MISO signal of the controller has been mapped with a single LED of the on-board 8bit LED unit and the resultant command responses and read/write data patterns were observed. Since the SPI mode is a serial bus interface mode, the SD card gives response serially through its output port to the master. The MISO line signal is left shifted in every clock cycle to observe a series of patterns in 8-bit LED unit available in the FPGA board. Additionally, in the output section, a clock down converter unit has been designed and integrated to slow down the speed of response of the controller for better perception. This is a little compromise with the speed of operation in testing and verification section. However, introduction of this section is purely optional and while integration of the controller with real-time high speed system this unit is to be omitted.

Test unit: DSO: A digital storage oscilloscope (DSO) has been connected with the input (MOSI) and the output (MISO) port of the controller. Both the output and input data patterns have been observed in DSO for further verification. The clock down converter unit has also been integrated here to slow down the response speed of the card. But, it is introduced only for the card read section for

all the cards and initialization section for the SDHC card only.

The results of the proposed controller have been observed and verified in chronological order as per problem description stated above.

Case I: result: pre-declared embedded data pattern: The first case study represents the complete three-state access of a cannon 16 MB SD card. The steps in different phases of data transfer are described below:

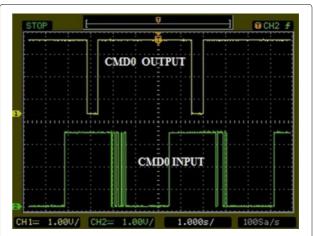

*Initialization* - Figures 19 and 20 show the initialization state output mapped in the on-board LEDs. The driving signal for the initialization module is the Reset signal. Figure 19 shows the output response pattern of the SD card after execution of the first command (CMD0). Figure 20 shows the output pattern after completion of the entire initialization step, when the card is in idle mode.

Card write operation - The pre-defined 8-bit embedded data pattern has been written to the SD card. Figure 21 shows the CRC status response (viz. "00000101") coming from SD card to the output port. The card responds to every successful write of an entire block. If the operation performed is a single block write, then the card gives the response once after the completion of the write operation of the entire block. But if it is a multiblock write operation, then the card responds after every block write completion, until the end block command (CMD12) has been issued.

Card read operation - Here, we consider an arbitrary data pattern, say e.g., "11010011" which has been read from the SD card. Figure 22 shows that data pattern on the LEDs. Both the single block and the multiblock write and read operations have been verified with the data pattern. This 8-bit data pattern has been written repeatedly to form the entire block (of 512 bytes) to perform the block write operation.

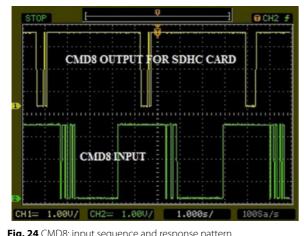

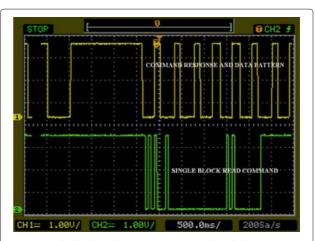

Case II: result: pseudo-random number sequences: The second case study represents the complete 3-state access for a SanDisk 8 GB class 4 SDHC card. Both the input and output ports are connected with the DSO. The study shows the efficiency of the proposed controller for high capacity SD card. Later on, the 16 MB Cannon SD card and the 2 GB microSD card have also been verified for the read/write process.

Fig. 19 CMD0 response pattern on the on-board LEDs for SD card

**Fig. 20** Initialization process completion response on the on-board LEDs for SD card

SDHC card - The results obtained for the 4 GB SanDisk SDHC card are described in this section.

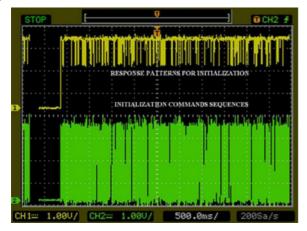

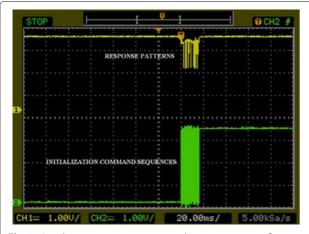

*Initialization* - Figures 23, 24, 25, 26 and 27 show the complete initialization process of the SDHC card. The initialization command and corresponding response pattern of the card have been recorded using DSO. In idle state, the proposed controller gives a logic high signal through the MOSI line and it also receives a logic high signal from the SDHC card.

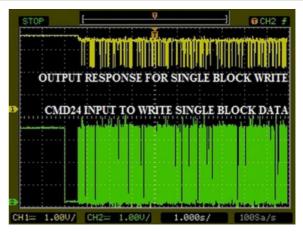

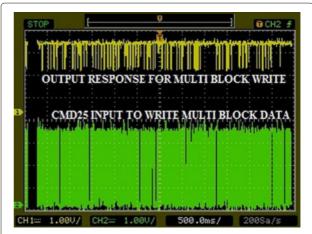

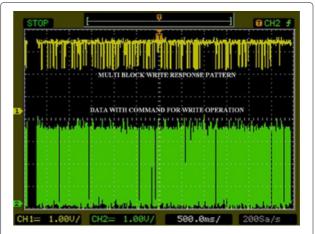

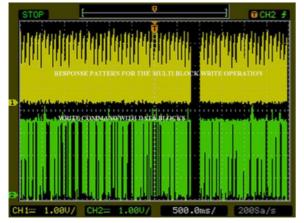

Card write operation - Figures 28 and 29 show the input and output pattern for write operation. The input data have been generated by a PRN generator. Both the single block and the multiblock data transfer operation have been performed. Figure 28 shows the input and output sequence of a single block write operation whereas Fig. 29 shows the multiblock write operation.

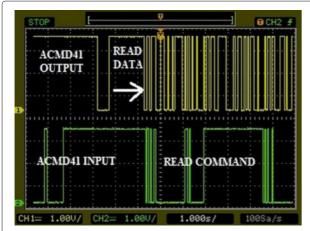

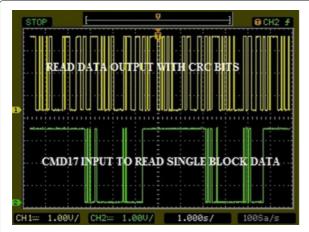

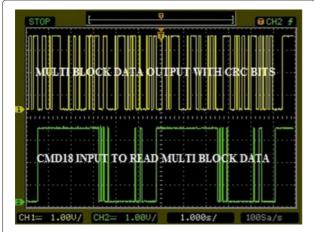

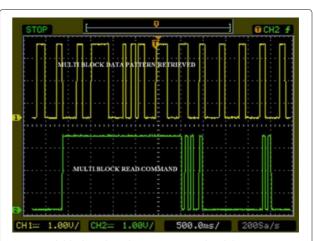

Card read operation - Figures 30 and 31 show the read operation of the card. The previously written data pattern, generated by PRN generator, has been read to verify the complete operational performance. Figure 30 shows the single block read operation and Fig. 31 shows the multiblock read operation.

SD card - The results obtained for the 16 MB Cannon SD card are described in this section. Figure 32 describes the complete initialization process. The clock divider section has not been introduced in this section. So the process operates in full clock as provided for the initialization of the SD card. To validate the data

Fig. 21 CRC response pattern for write operation

Fig. 22 Data pattern retrieved in read operation

transfer procedure, the multiblock write operation, shown in Fig. 33, has been performed for the PRN sequences. Later on, the data pattern has been retrieved from the SD card by performing both the single block and multiblock read operation. Figure 34 shows the single block read operation and Fig. 35 describes the multiblock read operation.

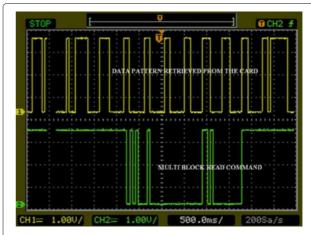

MicroSD card - The results obtained for the 2 GB microSD card are described in this section. The operation method and response patterns are nearly the same to the SD card. The microSD card initialization requires 100- to 400-KHz clock frequency. The clock divider module has not been integrated during initialization and block write phases. It has been used only for the read operation to make the validation process realizable. The multiblock read/write operation has been performed only to validate the data transfer operation. Figure 36 describes the complete initialization process. Figure 37 describes the multiblock write process and Fig. 38 indicates the multiblock read operation for the 2 GB microSD card.

Fig. 23 CMD0: input sequence and response pattern

Fig. 24 CMD8: input sequence and response pattern

Fig. 27 Idle mode input and response sequence

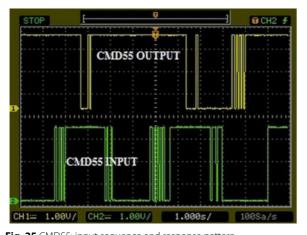

Fig. 25 CMD55: input sequence and response pattern

Fig. 28 Input data with response pattern for single block write operation on DSO

Fig. 26 ACMD41: input sequence and response pattern with single block read sequence

Fig. 29 Input data with response pattern for multiblock write operation on DSO

$\begin{tabular}{ll} \textbf{Fig. 30} Single block read mode input command and data response from SDHC \\ \end{tabular}$

$\begin{tabular}{ll} \textbf{Fig. 33} & \textbf{Input data} & \textbf{with response pattern for multiblock write} \\ \textbf{operation to SD card} \\ \end{tabular}$

$\begin{tabular}{ll} \textbf{Fig. 31} & \textbf{Multiblock} & \textbf{read mode input command and data response} \\ \textbf{from SDHC} \\ \end{tabular}$

$\begin{tabular}{ll} \textbf{Fig. 34} Single block read mode input command and data response from SD \\ \end{tabular}$

Fig. 32 Initialization: input sequences and response patterns

$\textbf{Fig. 35} \ \text{Multiblock} \ \text{read mode input command and data response} \\ \text{from SD}$

**Fig. 36** Initialization: input sequences and response patterns for microSD card

**Fig. 38** Multiblock read mode input command and data response from microSD

The third and the forth case study were to test and verify the efficiency of the proposed controller for real-time audio and video signal storage and retrieval.

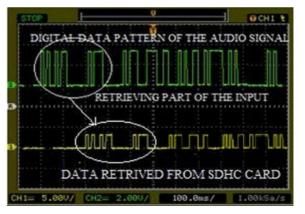

Case III: result - audio signal transmission: In this study an analog signal is fed to the system in audio range. The received signal has been converted and compressed into 8-bit digital data pattern and fed it to the input data bus of the controller for the verification of multiblock data write procedure in the SDHC card. The data stored in this process is again accessed via multiblock card read procedure of the controller. Both the input audio data and the data accessed from the SDHC card were fed to the DSO. Figure 39 shows the input data pattern and the read operation from the SDHC card. The read and write operations are two different operations which cannot be performed at same time instance. Therefore, initially the analog signal was converted and stored into the SDHC card and during

that phase different commands, responses and data patterns were recorded using DSO. Later on, the same data pattern has been retrieved from the SDHC card in read mode and they were also recorded. We got the stored data back along with the CRC bits and on DSO those CRC patterns were present with the original data. For simplicity, the result has been given in the form of bit pattern and the parts of the stored data have been encircled to show the same portion of the retrieved data.

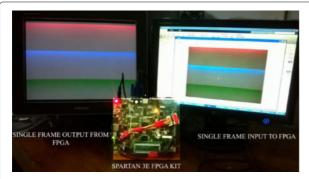

Case IV: result - video signal transmission: The video signal has been stored and retrieved in this fourth case study. A video signal of 20 frames/second was fed to the system and subsequently stored into the card. The SanDisk 8 GB class 4 SDHC card has been used to verify the video signal transmission process. The card performs in 4 MB/s writing speed to store and retrieve the video signal. The entire communication was governed under the control of the proposed controller. To ensure the successful data storage and retrieval, later those frames were retrieved from

**Fig. 37** Input data with response pattern for multiblock write operation to microSD card

Fig. 39 Audio signal processing: data stored and retrieval pattern

the card and they were displayed in CRT monitor. The retrieved frames were compared with the original frames which were stored in the card. Figure 40 shows a snapshot of such video data storage and retrieval. The right hand screen in Fig. 40 shows the actual frame that was written in the card and the left hand side monitor shows the frame retrieved from the card. Here the left hand side monitor, the implemented controller along with the card work as a standalone unit.

Case V: result - dataset from MSR Cambridge Traces: The datasets were collected from MSR Cambridge traces [24, 25], as explained in "Case studies" section where the description of the datasets is illustrated. In our experimental part, each file of three traces is considered as separate dataset. The datasets were divided into multiple blocks so that we can accomplish multiblock read-write with respect to flash memory. In the performance comparison section, the metrics were computed for multiblock data read write with respect to different I/O traces. Results were tabulated for the datasets collected from the repositories.

Case VI: result - dataset from UMass Trace Repository: The datasets were collected from UMass Trace Repository [24, 27], as explained in "Case studies" section. In our experimental part, those datasets have been divided into multiple blocks and the data has been stored in San-Disk 8 GB class 4 SDHC card to accomplish multiblock read-write. In the performance comparison section, the metrics were computed for multiblock data read write with respect to different I/O traces. Results were tabulated for the dataset collected from the repositories.

Case VII: result - dataset from SNIA Iotta Repository Historical Section: The datasets were collected from the historical section SNIA Iotta Repository [24, 26], as explained in "Case studies" section. In our experimental part, those datasets have been divided into multiple blocks to accomplish the read write with respect to flash memory. Results were tabulated for the dataset collected from the repositories.

Fig. 40 Snapshot of video processing

### 6 Performance comparison

This section describes the performance comparison of the controller with reported results. The logic utilization for the proposed controller is only 5% of the total logic present in Spartan 3E FPGA board. This is evident from Table 6.

The proposed controller has been tested for a single block as well as for multiblock (5000 block) data read and write operation for the SD, SDHC, and microSD cards. Table 11 shows a summary of clock cycle elapsed by SDHC card, and Table 12 shows a summary of clock cycle elapsed by the microSD card during initialization, single and multiblock reads, and single and multiblock write operation. In the initialization phase, the proposed system utilizes full bandwidth supported by SD card technology. Initially the SDHC card receives CMD0, CMD8, CMD55, ACMD41, CMD58, and CMD16 commands and the controller receives corresponding responses for each of the commands. (CMD55 and ACMD41) pair of commands may be required to send "n" times until the card generates the response pattern x"00". Therefore the total number of clock cycles elapsed in initialization phase by SDHC card is 112(2 + n). However in Table 11 we have considered the ideal case of n = 1, and the initialization process takes the minimum of 336 clock cycles for SanDisk 8 GB class 4 SDHC card in SPI bus mode. Similarly, SD card initialization process requires 56(3 + 2n)clock cycles and microSD card requires 56(1 + 2n) clock cycles for initialization. The difference is due to the fact that CMD58 command is not necessary for the initialization phase of SD card and CMD58, CMD16 commands are not required for the microSD card initialization. Only CMD0 and (CMD55+ACMD41) in place of CMD1 initiates the microSD card in SPI mode. In the ideal case with n = 1, the initialization process takes the minimum of 280 clock cycles for cannon 16 MB class 2 SD card and 168 clock cycles for microSD card in SPI bus mode. The HCS bit should be high in ACMD41 command for initialization of the SDHC card, whereas for SD card and the microSD card with capacity ≤ 2 GB requires HCS bit to be de-asserted at the time of initialization.

Tables 13 and 14 show a comparative study of the speed of response for SD card. Also in Table 13, the initialization time for SDHC card and microSD card has been

Table 11 Clock cycles achieved for SDHC

| Process                 | CCTPP    |

|-------------------------|----------|

| Initialization          | 336      |

| Single block read       | 4176     |

| Single block write      | 4184     |

| Multiblock (5000) read  | 20600056 |

| Multiblock (5000) write | 20640056 |

Table 12 Clock cycles achieved for microSD card

| Process                 | CCTPP    |

|-------------------------|----------|

| Initialization          | 168      |

| Single block read       | 4176     |

| Single block write      | 4184     |

| Multiblock (5000) read  | 20600056 |

| Multiblock (5000) write | 20640056 |

reported. Here the comparison is only done with respect to SD card initialization time available in the literature. Also from Table 14, we find the percentage increase in speed of response in read-write phase for SD card with the proposed controller.

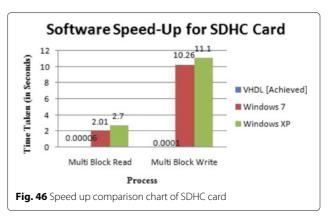

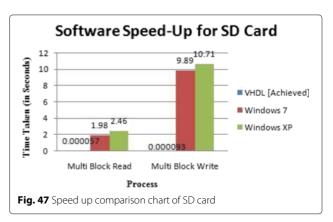

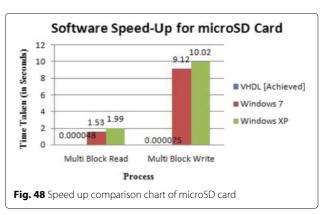

Table 15 shows the software speed-up for the proposed controller. The SanDisk 8 GB class 4 SDHC card, Cannon 16 MB class 2 SD card, and the class 4 microSD card have been used for multiblock data transfer using the proposed controller, designed in VHDL. The similar data transfer setup has been implemented based on two modern operating systems (Windows 7 and Windows XP (Service Pack 3)) to validate the speed up of the proposed controller with respect to existing software based approaches. The modern operating systems are mostly written in JAVA or a high-level languages which ultimately makes the system's in-build controller slower than the proposed controller, optimized using VHDL. The computer used for this purpose contains Intel second-generation dual core processor, 2 GB DDR3 RAM as the basic specifications.

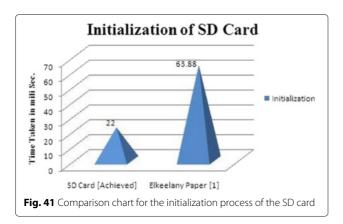

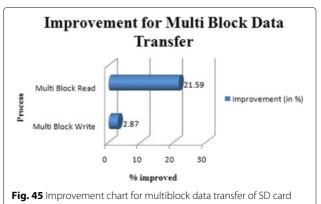

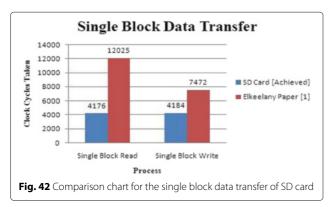

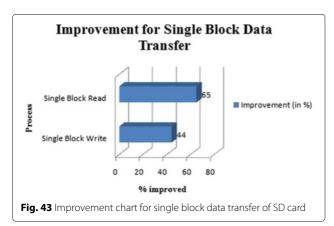

Figure 41 shows the comparison chart of the initialization process performed in the SD card. The work has been compared with the closest work reported in Elkeelany et al's paper [1]. The chart in Fig. 41 clearly shows the reduction in the initialization time. The proposed process introduces 65.56% improvement in the initialization time. Figure 42 describes the comparison in clock cycle required for single block data transfer (single block read/write) and Fig. 43 shows the corresponding improvements in percentage. The proposed architecture introduces 65% improvement of clock cycle for single block read and 44% improvement of clock cycle for single block write operation. On the other hand, Fig. 44 explains the comparison in multiblock data transfer and Fig. 45 shows corresponding improvement in percentage. Here, the proposed system introduces 21.59% improvement in required clock cycle for multiblock read and 2.87% improvement

Table 13 Speed comparison in initialization phase

|                |          | TTPP         |          |          |

|----------------|----------|--------------|----------|----------|

| Process        | SD card  | O. Elkeelany | SDHC     | MicroSD  |

|                | achieved | et al. [1]   | achieved | achieved |

| Initialization | 22 ms    | 63.88 ms     | 27 ms    | 20 ms    |

**Table 14** Speed comparison in read/write phase

|                               |                     | CCTPP                   |             |

|-------------------------------|---------------------|-------------------------|-------------|

| Process                       | SD card<br>achieved | Elkeelany<br>et al. [1] | % Reduction |

| Single Block Read             | 4176                | 12025                   | 65          |

| Multiblock Read (5000 Block)  | 20600056            | 26275000                | 21.59       |

| Single Block Write            | 4184                | 7472                    | 44          |

| Multiblock Write (5000 Block) | 20640056            | 21250000                | 2.87        |

in required clock cycle for multiblock write. The speed of SD card data access in terms of clock cycles for single block read/write is increasing to 65 and 44%, respectively, and for multiblock read write it is increasing to 21.59 and 2.87%, respectively. The comparison chart of the software speed-up of VHDL with respect to the high-level language is shown in Figs. 46, 47 and 48 for SDHC, SD and microSD card, respectively.

The performance of the proposed controller has also been tested for three different commonly used repositoties. These three repositories are MSR Cambridge Traces [25], UMass Trace Repository [27], and SNIA Iotta Repository [26]. Tables 8, 9 and 10 represent the characteristics of MSR Cambridge Traces [25], UMass Trace Repository [27], and SNIA Iotta Repository [26], respectively. The files in each repositories, the size of the file, and the attributes of the files are given in the tables. Tables 16, 17 and 18 show the performance of the controller for both read and write process with respect to repository datasets and workload, average CCTPP(read), average CCTPP (write), and IOPS metrics. All the datasets of MSR cambridge and UMass repositories have been used and only Harvard SOS subtraces of NFS trace of SNIA lotta repository has been used for experimental section.

**Table 15** Software speedup in multiblock data transfer phase

|           |                                   | TTPP          |           |            |

|-----------|-----------------------------------|---------------|-----------|------------|

| Card used | Process                           | VHDL achieved | Windows 7 | Windows XP |

| SDHC      | Multiblock read<br>(5000 blocks)  | 60 μs         | 2.01 s    | 2.70 s     |

|           | Multiblock write<br>(5000 blocks) | 100 μs        | 10.26 s   | 11.10 s    |

| SD        | Multiblock read<br>(5000 blocks)  | 57 <b>μ</b> s | 1.98 s    | 2.46 s     |

|           | Multiblock write<br>(5000 blocks) | 93 μs         | 9.89 s    | 10.71 s    |

| MicroSD   | Multiblock read<br>(5000 blocks)  | 48 μs         | 1.53 s    | 1.99 s     |

|           | Multiblock write<br>(5000 blocks) | 75 μs         | 9.12 s    | 10.02 s    |

**Table 16** Performance table for MSR Cambridge Repository [25]

| Repository name | File name abbreviation | Workload in blocks of data | Average response CCTPP (Read) | Average response CCTPP (Write) | IOPS<br>(operations/second) |

|-----------------|------------------------|----------------------------|-------------------------------|--------------------------------|-----------------------------|